CSR A6 硬件设计指导文档文档格式.docx

CSR A6 硬件设计指导文档文档格式.docx

- 文档编号:7608218

- 上传时间:2023-05-08

- 格式:DOCX

- 页数:13

- 大小:574.18KB

CSR A6 硬件设计指导文档文档格式.docx

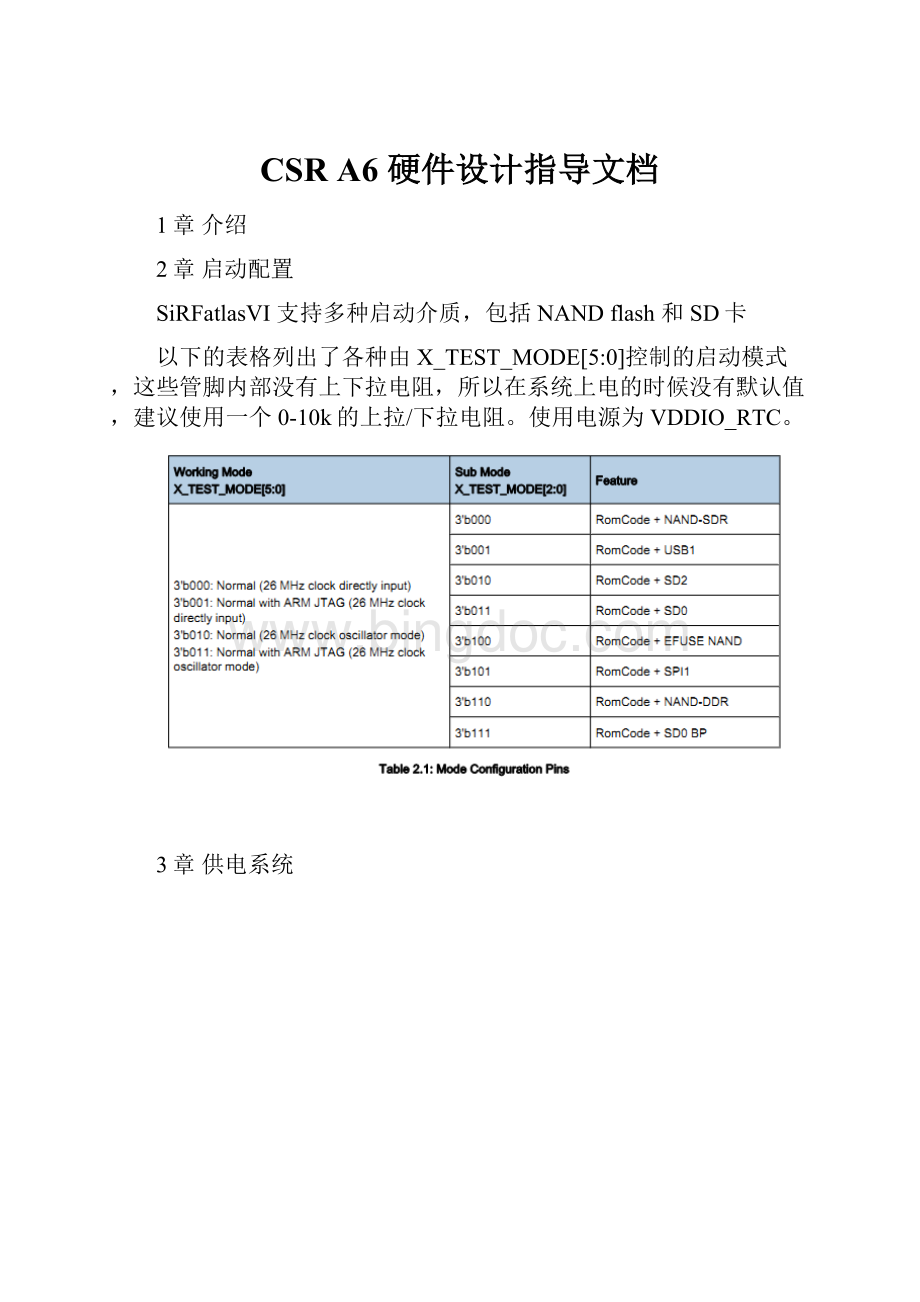

《CSR A6 硬件设计指导文档文档格式.docx》由会员分享,可在线阅读,更多相关《CSR A6 硬件设计指导文档文档格式.docx(13页珍藏版)》请在冰点文库上搜索。

17个100nF/0402MLCC滤波电容对VDD_CORE进行滤波

12个220nF/0402MLCC电容对VDDIO_MEM

其他的电源使用100nf的滤波电容进行滤波。

4章储存器

特征

支持DDR2/DDR3/LPDDR2器件

16位数据模式

支持高达512MB,A14和CS1同用.

支持时钟为400MHZ的DDR2/DDR3

支持时钟频率为333MHZ的LPDDR2.

支持1.35V/1.5V的DDR3的所有指令。

支持ODT功能

工作模式

数字锁相环锁环/失锁模式;

DDR3/LPDDR2模式;

低电压模式开关状态;

4.1原理图设计

4.3PCBlayout指导

1,分组:

数据组,地址组,

2,滤波以及电源走线。

3,SI方面走线注意事项,3W原则,参考平面,阻抗控制等

4,误差控制

4.4六层/八层板的layout指导

4.5测试点设计

在接收端进行测试设计,尤其是对读,写网络的测试。

测试点必须放在靠近接收端,并且避免干扰。

差分对的测试点设计,在测试点附近放置地测试点/过孔,保证回流。

5章UART1

对于使用NANDflash和SD卡进行引导多媒体时,使用UART1下载非引导图像数据,这就意味着UART1必须用来做NANDflash和SD卡启动模型的调试接口

UART1的TXD/RXD管脚可以和SB1的DP/DM管脚复用,当X_USBONL为低电平时UART1信号可以通过USB1端口这是通过判定是否使用USB(高电平,还是使用UART1(低电平),在这里USB只能是从机模式。

只有当X_USBONL为高电平时USB的信号才可以通过USB1端口。

6章I2C

信号线上接4.7K的上拉电阻。

如果在I2C总线上接有多个I2C器件,保证这些器件同时上/掉电。

否则总线被占用着。

8章USB

对地阻抗90欧姆

在USB网络加上必要的EMD器件。

9章TSC/ADC

PCBlayout指导

模拟走线尽量短。

所有的模拟电路网络使用AGND作为参考地,特别是单端信号。

处理输入走线的时候特别需要注意,任何的噪声耦合都被当做输入信号,由此会降低ADC的动态范围。

所有参考线,等电平走线,电源走线尽量宽,为了保证走线的阻抗和增大走线宽度,可能需要进行隔层参考。

在进行换层的时候,多打过孔。

10章SD/多媒体

SD0/1采用SD和NAND_flash共用,只有SD2是全接口。

SD3和SPI共用,SD5和GPS共用,SD5有一个固定的电源域

所有SD信号都必须外加一个10k至100k的上拉电阻(开漏接口)。

SD在3.0V时支持高达50m的时钟频率。

和数据以及CMD信号相连的上拉电阻必须接到SD电源上,所有的SD/MMC芯片都必须在系统掉电后1ms内保持低于0.5V,否则在系统配置启动后将不会别识别,所有建议使用快速充电UC,例如AAT4280ICU-3-T1.

使用MMC4.4芯片作为boot时,将X_SD_VCC_ON_0连接到MMC芯片的复位管脚。

11章视频输出

所有信号走线等长

12章LCD

所有信号线等长。

13章振荡电路

注:

在设计时进行模式选择和晶体选型需参考各个端口电压。

错误的模式选择和器件选型会对XIN损坏。

在晶振电路中的电容需要满足振荡的基频,具体可以通过

计算

其中:

C1,C2是电路中的电容,Cs是3.5pF.

电容,晶体,电阻会对其他信号产生干扰,所以尽量摆在一起,晶体输出信号必须通过C1C2才可以进入芯片管脚。

振荡电路下面保证地平面的完整,并进行包地处理,在晶体下方打地孔确保回流路径。

14章复位

在RTC电源稳定后保持x_rtc_rst至少400ms的低电平,以保证RTC复位

复位源

1,上电复位,系统上电后,电源管理器产生复位信号系统复位。

2,软件复位,软件控制,复位后,外部存储器自行更新,大部分功能模块复位

3,热复位(调试口),看门狗复位,效果和软件复位一样。

4,图像/多媒体复位,

15章通用I/O口

GPIO口有两种情况

1,和LCD共用

没有高电平输入误差限度

没有自动防护装置

默认为输入

2,和其他功能共用

3.3V自动防护

5V的容差为3.3V在这种情况下需要串接一个33欧姆的电阻

3.3V的容差为2.8V,18.V

3GPIO0~GPIO3和GPIO[6]为RTC电源域。

4,VDDIO_N,VDDIO_LandVDDIO_SD2和VDDIO同时开/关防止发生开漏。

5,当状态保持功能开启的时候,一下情况是不能一同激活的

输入为上拉状态,但是PAD被另外一个芯片强迫低/高电平

输出为高时,但是PAD被另外一个芯片强迫低/高电平

输出为低时,但是PAD被另外一个芯片强迫高电平

16章音频

16.1音频控制相关管脚

16.2音频电路设计

1,提供2W输出功率

2,A6输出端到PA之间设计一个带通滤波器进行滤波。

电路如下

分析:

R1,C1组成一个F=1/2Pi*RC=86KHZ的低通滤波器,R2,C2组成一个截止频率为33KHZ的高通滤波器。

则通过的带宽为33K~86KHZ。

而DAC固定采样频率为44K,

16.3音频ADC的电路设计

为了防止信号的跳动在输入端口添加一个10K的电阻。

16.4PCBlayout指导

1,把音频部件尽量在同一层上靠近摆放,“一”字形摆放,远离高频信号,数字区,远离干扰源(开关电源等)

2,把microphones摆放在远离噪声源例如强驱动器(风扇,卡片驱动,扬声器,硬盘)。

3,音频走线时尽量走在同一层,而且走线宽度为12mil,确保音频走线下面至少有一个地平面和其他数字信号隔离,如果没有地平面则需要进行包地处理。

4,在走差分输出信号线的时候,两根信号(N/P)尽量靠近,走单端走线的时候满足3w原则,为了确保输出功率输出走线尽量宽,推荐走20mil。

5,功率控制回路走线尽量加粗,回路尽量小。

6,音频供电系统确保通过严格滤波,保证电流过流能力(功率保证)。

7,所有音频走线在模拟区。

17章NAND_flash

17.1NAND_flash断电硬件设计

使用条件:

确保在系统运行时候不会突然掉电。

或者保证在芯片电源掉电后保证不少于5ms的高电平(>

2.7V)并且保证NAND的WP管脚保持高电平。

对于一个4K的页容量的芯片,C167必须为100uf。

(?

?

)

17.2NAND写保护

在上电和掉电期间WP保持高电平。

当上电和电压保持正常时WP电平主要由VDD_flash通过R923提供以保证>

2.7V,当掉电的时候:

当:

VDD_flash>

2.7时有VDD_flash通过R923保证电压,当VDD_flash<

2.7V时,由VDD_flash通过R923和电容C917放电通过U901共同提供。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- CSR A6 硬件设计指导文档 硬件 设计 指导 文档

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《安全在我心中生命在我手中》主题班会教案.docx

《安全在我心中生命在我手中》主题班会教案.docx