SOC设计方法与实现实验报告Word下载.doc

SOC设计方法与实现实验报告Word下载.doc

- 文档编号:468298

- 上传时间:2023-04-29

- 格式:DOC

- 页数:27

- 大小:489.50KB

SOC设计方法与实现实验报告Word下载.doc

《SOC设计方法与实现实验报告Word下载.doc》由会员分享,可在线阅读,更多相关《SOC设计方法与实现实验报告Word下载.doc(27页珍藏版)》请在冰点文库上搜索。

b.(3)中经数字滤波的信号,在转换成十进制并做七段译码后,百位经端口d00,十位经端口d10,个位经端口d01送出;

c.(3)中经数字滤波的信号,在经过压缩后通过端口ap送出。

5.2:

数字滤波器

数字滤波器的转移函数为:

滤波器的系数B0,B1,...,B6均由微处理器给出。

微处理器可以根据需要修改这些系数。

5.2:

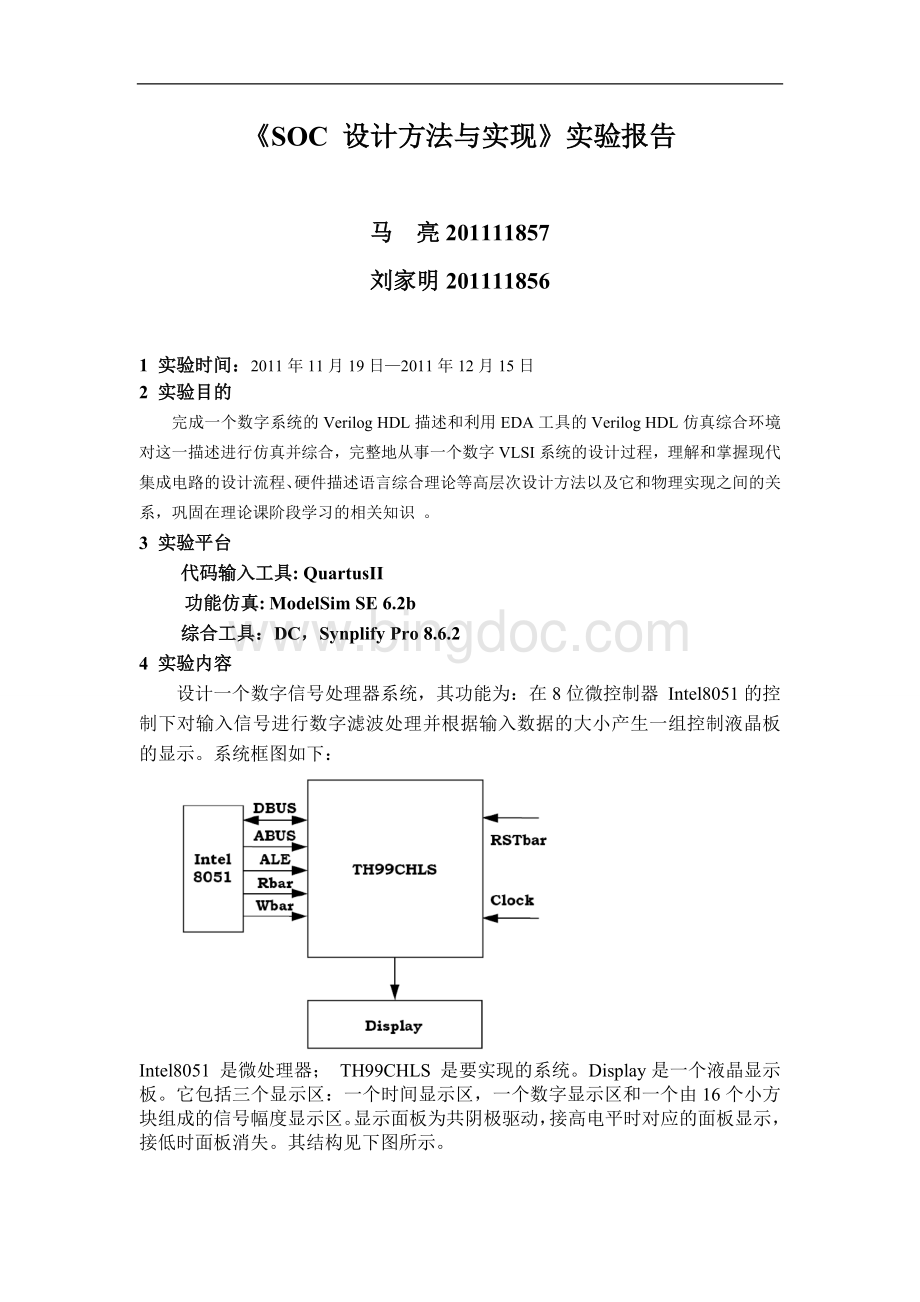

系统模块说明和代码说明:

根据功能分析,将整个系统分为8个模块。

各个模块对应的源文件和功能描述如下表所示。

模块名称

对应源文件

功能说明

decoder

decoder.v

将四位二进制译码为LED显示。

输入4bit,输出为7bit直接驱动显示装置,为组合逻辑。

H2D

H2D.v

进行16进制到十进制的转换。

输入为8bit无符号数,输出为百,十,个位数字(其中每个数字4bit位宽),同样为组合逻辑

decoder_4X16

4-16译码器,主要是将经过y=sqrt(x)压缩后的数据送至显示设备。

输入4bit,输出16bit,组合逻辑。

sqrt_lut

sqrt_lut.v

主要实现y=sqrt(x)的运算。

主要是通过比较和查找表方式实现。

输入8bit,输出4bit。

时序逻辑,一个时钟周期。

mul8b_shiftadd_fsm

mul8b_shiftadd_fsm.v

乘法器设计。

通过移位加的方式实现。

内部通过状态机实现。

完成一次乘法需要8个时钟周期

timer_clk

timer_clk.v

时间时钟模块,主要是根据系统时钟计算秒。

通过计数器级联的方式实现。

filter

filter.v

这是整个系统比较核心的部分。

主要实现滤波器的设计和与微处理器的接口时序设计。

接口需要三态控制,并且要注意读写信号的控制,滤波器采用并行设计,用面积换取速度。

TH99CHLS

TH99CHLS.v

顶层元件例化。

主要是将上述各个模块进行组合。

整个功能框图如下:

6:

代码功能测试

下面是测试用的模块介绍,模拟TH99CHLS外围的单片机、控制信号和数据输入等:

对应的源文件

osc_rst

osc_rst.v

产生时钟频率和复位信号

fir_tb

fir_tb.v

滤波器数据的输入

wr_rd

wr_rd.v

单片机WR,RD信号的模拟

mcu

mcu.v

主要是模拟单片机对TH99CHLS芯片的控制,包括寄存器的读入与读出等一系列操作

top_test

top_test.v

顶层测试文件,主要是进行元件例化

ModelSimSE功能仿真结果波形图如下:

第一张图为前0-7us,第二张图为7us-15us.详细图形见source中的1.bmp和2.bmp.也可以查看其下的vsim.wlf(需要安装modelsim)。

此图为对TH99CHLS芯片内部b0-b6(滤波器系数)寄存器的操作和对mini,hour寄存器初始化的操作仿真结果。

7:

综合结果及分析

Synplify综合结果如下:

DC综合结果如下:

8:

所占用的资源和数据通道分析

该系统所占用的资源如下:

在滤波器设计中,并没有采用乘法器的复用,而是采用了多个乘法器的复制,牺牲面积来换取速读的提高。

综合后的频率能够达到50MHz。

滤波器的数据通道如下:

(用多个乘法器)

9:

VerilogHDL代码

///////////////////////////////////////////////////////////////////////////////////

`timescale1ns/10ps

moduletop_test();

wireclk,rst_n;

wire[7:

0]abus;

wireale,rbar_n,wbar_n,cs_n;

wirepebar_n;

0]fir_in;

wire[7:

0]dbus_xio;

wire[13:

0]hour,mini;

wire[20:

0]fir_out;

wire[15:

0]fir_out_sqrt;

wiresend_data_en;

fir_tbUfir_tb(send_data_en,pebar_n,fir_in);

osc_rstUost_rst(clk,rst_n);

TH99CHLSUTH99(

dbus_xio,

abus,

rbar_n,

wbar_n,

ale,

pebar_n,

fir_in,

cs_n,

rst_n,

clk,

//outputports

fir_out,

fir_out_sqrt,

hour,

mini

);

mcuUmcu(

.dbus_xio(dbus_xio),

.abus(abus),

.rbar_n(rbar_n),

.wbar_n(wbar_n),

.ale(ale),

.cs_n(cs_n),

.send_data_en(send_data_en)

);

endmodule

//////////////////////////////////////////////////////////////////

moduledecoder(

//input

hex,

//output

led

);

input[3:

0]hex;

outputreg[6:

0]led;

always@(hex)begin

case(hex)

4'

b0000:

led=7'

b011_1111;

//0

b0001:

b001_1000;

//1

b0010:

b111_0110;

//2

b0011:

b111_1100;

//3

b0100:

b101_1001;

//4

b0101:

b110_1101;

//5

b0110:

b110_1111;

//6

b0111:

b011_1000;

//7

b1000:

b111_1111;

//8

b1001:

b111_1101;

//9

default:

b000_0000;

//null

endcase

end

////////////////////////////////////////////////////////////////////

moduleTH99CHLS(

//input

inputclk,rst_n;

input[7:

inputale,rbar_n,wbar_n,cs_n;

inputpebar_n;

inout[7:

output[13:

output[20:

output[15:

wire[15:

0]fir_out_Hex;

wire[7:

0]hour_Hex,mini_Hex;

wire[3:

0]fir_sqt_Hex;

0]hud_Hex,ten_Hex,num_Hex;

filterUfilter(.dbus_xio(dbus_xio),.abus(abus),.rbar_n(rbar_n),

.wbar_n(wbar_n),.ale(ale),.pebar_n(pebar_n),

.fir_in(fir_in),.cs_n(cs_n),.rst_n(rst_n),.clk(clk),

.fir_out(fir_out_Hex),.hour(hour_Hex),.mini(mini_Hex));

sqrt_lutUsqt(.result(fir_sqt_Hex),.in(fir_out_Hex[7:

0]),.clk(clk),.rst_n(rst_n));

decoder_4X16Ude4X16(.out(fir_out_sqrt),.in(fir_sqt_Hex));

H2DUH2d1(.hex(fir_out_Hex[7:

0]),

.hud(hud_Hex),.ten(ten_Hex),.num(num_Hex));

decoderUdecoder1(.hex(hud_Hex),.led(fir_out[20:

14]));

decoderUdecoder2(.hex(ten_Hex),.led(fir_out[13:

7]));

decoderUdecoder3(.hex(num_Hex),.led(fir_out[6:

0]));

decoderUdecoder4(.hex(hour_Hex[7:

4]),.led(hour[13:

decoderUdecoder5(.hex(hour_Hex[3:

0]),.led(hour[6:

decoderUdecoder6(.hex(mini_Hex[7:

4]),.led(mini[13:

decoderUdecoder7(.hex(mini_Hex[3:

0]),.led(mini[6:

//////////////////////////////////////////////////////////////////////

`timescale1ns/10ps

modulewr_rd(

dbus_xio,

abus,

rbar_n,

wbar_n,

ale);

parameterMCU_CLK=40;

//25MHz

parameterLL_DELAY=15;

outputreg[7:

outputregale,rbar_n,wbar_n;

inout[7:

regctrl;

reg[7:

0]abus_low;

assigndbus_xio=ctrl?

abus_low:

8'

hzz;

//ifctrl=1outputthenhiz

integeri;

initialbegin

rbar_n=1'

b1;

wbar_n=1'

taskwrite_register;

input[7:

0]write_addr;

0]write_data;

//writemovx

begin

ale=1'

b0;

//configb0

#MCU_CLK;

ctrl=1'

#LL_DELAY;

abus_low=write_addr;

abus=8'

h0;

ale=0;

//float

abus_low=write_data;

#1;

wbar_n=1'

for(i=0;

i<

8;

i=i+1)

endtask

//endmovx

taskread_register;

0]read_addr;

output[7:

0]read_data;

//readmovx

abus_low=read_addr;

rbar_n=1'

read_data=dbus_xio;

7;

endtask

/////////////////////////////////////////////////////////////////////

moduledecoder_4X16(

//output

out,//16bitwidthhighvoltageffect

//input

in//fourbitwidth

);

0]in;

output[15:

0]out;

assignout[15]=in[3]&

in[2]&

in[1]&

in[0];

//111115

assignout[14]=in[3]&

(~in[0]);

//111014

assignout[13]=in[3]&

(~in[1])&

//110113

assignout[12]=in[3]&

//110012

assignout[11]=in[3]&

(~in[2])&

//101111

assignout[10]=in[3]&

//101010

assignout[9]=in[3]&

//10019

assignout[8]=in[3]&

//10008

assignout[7]=(~in[3])&

//01117

assignout[6]=(~in[3])&

//01106

assignout[5]=(~in[3])&

//01015

assignout[4]=(~in[3])&

//01004

assignout[3]=(~in[3])&

//00113

assignout[2]=(~in[3])&

//00102

assignout[1]=(~in[3])&

//00011

assignout[0]=(~in[3])&

//00000

endmodule

modulefilter(

//inputports

mini,

inoutwire[7:

//databusconnecttop0complexofdataandaddr

//outputreg[7:

0]dbus;

input[7:

//addrbusconnecttop2

inputrbar_n,wbar_n;

//rdandwrsignalconnecttord,weofmcu

inputale,cs_n;

inputpebar_n;

inputclk,rst_n;

outputreg[15:

output[7:

/**********************///aboutconfig

0]B0,B1,B2,B3,B4,B5,B6;

0]mcu_num;

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- SOC 设计 方法 实现 实验 报告

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

二年级下册数学专项练习-应用题1.docx

二年级下册数学专项练习-应用题1.docx

中考语文综合探究专题复习用.ppt

中考语文综合探究专题复习用.ppt