TMS320C28x系列DSP芯片结构及引脚功能文档格式.docx

TMS320C28x系列DSP芯片结构及引脚功能文档格式.docx

- 文档编号:408522

- 上传时间:2023-04-28

- 格式:DOCX

- 页数:47

- 大小:62.59KB

TMS320C28x系列DSP芯片结构及引脚功能文档格式.docx

《TMS320C28x系列DSP芯片结构及引脚功能文档格式.docx》由会员分享,可在线阅读,更多相关《TMS320C28x系列DSP芯片结构及引脚功能文档格式.docx(47页珍藏版)》请在冰点文库上搜索。

?

“S”是温度选择(-40C〜+125C)的特征化数据,仅对TMS是适用的。

产品预览(PP):

在开发阶段的形成和设计中与产品有关的信息,特征数据和其他规格是设计的目标。

TI保留了正确的东西,更换或者终止了一些没有注意到的产品。

高级信息(AI):

在开发阶段的取样和试制中与新产品有关的信息,特征数据和其他规格用以改变那些没有注意到的东西。

产品数据(PD):

是当前公布的数据信息,产品遵守TI的每项标准保修规格,但产品加工不包

括对所有参数的测试。

TMP:

最终的硅电路小片,它与器件的电气特性相一致,但是没有进行全部的品质和可靠性检测。

C28x系列芯片的主要性能如下。

1.高性能静态CMOS(StaticCMOS)技术

150MHz(时钟周期6.67ns)(最大)

低功耗(核心电压1.8V,I/O口电压3.3V)

Flash编程电压3.3V

2.JTAG边界扫描(BoundaryScan)支持

3.高性能的32位中央处理器(TMS320C28x)

16位X16位和32位X32位乘且累加操作

16位X16位的两个乘且累加

哈佛总线结构(HarvardBusArchitecture)

强大的操作能力

迅速的中断响应和处理

统一的寄存器编程模式

可达4兆字的线性程序地址

可达4兆字的数据地址

代码高效(用C/C++或汇编语言)

与TMS320F24x/LF240x处理器的源代码兼容

4.片存储器

8KX16位的Flash存储器

1KX16位的OTP型只读存储器

L0和L1:

两块4KX16位的单口随机存储器(SARAM)

H0:

一块8KX16位的单口随机存储器

M0和M1:

两块1KX16位的单口随机存储器

5.根只读存储器(BootROM)4KX16位

带有软件的Boot模式

标准的数学表

6.外部存储器接口(仅F2812有)

有多达1MB的存储器

可编程等待状态数

可编程读/写选通计数器(StrobeTiming)

三个独立的片选端

7.时钟与系统控制

支持动态的改变锁相环的频率

片振荡器

看门狗定时器模块

&

三个外部中断

9.外部中断扩展(PIE)模块

可支持96个外部中断,当前仅使用了45个外部中断

10.128位的密钥(SecurityKey/Lock)

保护Flash/OTP和L0/L1SARAM

防止ROM中的程序被盗

11.3个32位的CPU定时器

12•马达控制外围设备

两个事件管理器(EVA、EVB)

与C240兼容的器件

13.串口外围设备

串行外围接口(SPI)

两个串行通信接口(SCIs),标准的UART

改进的局域网络(eCAN)

多通道缓冲串行接口(McBSP)和串行外围接口模式

14.12位的ADC,16通道

2X8通道的输入多路选择器

两个采样保持器

单个的转换时间:

200ns

单路转换时间:

60ns

15.最多有56个独立的可编程、多用途通用输入/输出(GPIO)弓|脚

16.高级的仿真特性

分析和设置断点的功能

实时的硬件调试

17.开发工具

ANSIC/C++编译器/汇编程序琏接器

支持TMS320C24x/240x的指令

代码编辑集成环境

DSP/BIOS

JTAG扫描控制器(TI或第三方的)硬件评估板

18.低功耗模式和节能模式

支持空闲模式、等待模式、挂起模式

停止单个外围的时钟

19.封装方式

带外部存储器接口的179球形触点BGA封装

带外部存储器接口的176引脚低剖面四芯线扁平LQFP封装没有外部存储器接口的128引脚贴片正方扁平PBK封装

20.温度选择

A:

-40C~+85C

-40'

C~+125C

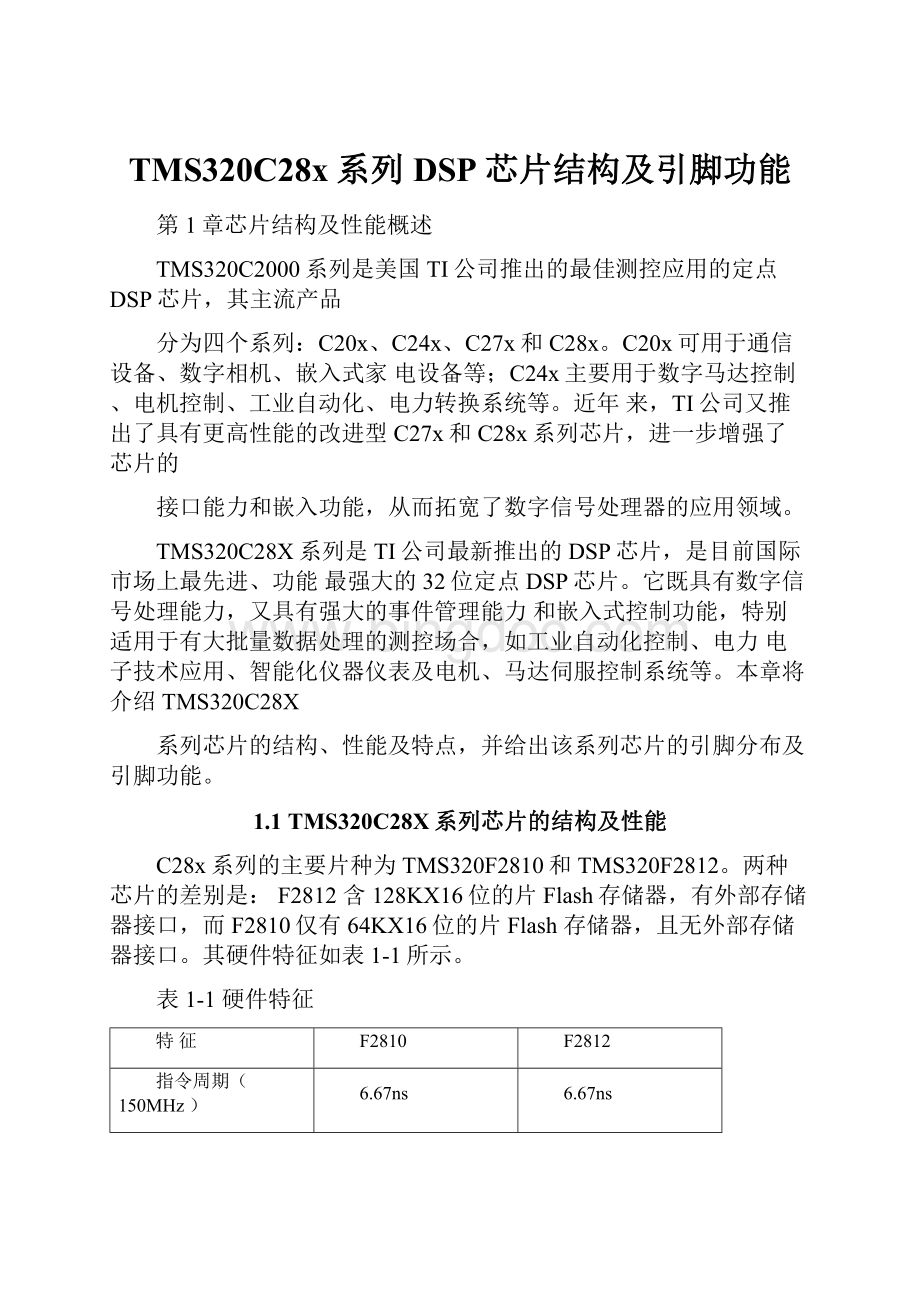

C28x系列芯片的功能框图如图1-1所示。

[[XI

PIE

粧中斷>

FPii進吋斛0

「PU”定时轟1

CPU*磁时器】

"

%丁2

l\IU

1KT[I2;

L]

(MN门}

悝JM~\

1f地址(I旳、

XINTI3

KNMJ

GPI(t.rioiW)°

孙部中勵控制陽(XINT1/l/n.XNMl>

9C1A/SCIB

FIFO

SPI

McBSP

UK)

cCA\

FVATVF4

\

厲通蔚—〉12^(AfX'

O

XRS

XIAtLKl\

X2

xrxpt[n(s

和卩LL外部时钟

-I-

低功换块

看门狗)

■*RS

—CLKIM

O

■J毗器启戈

M4SAKAX1IKX|6

Ml聃RAM

IKxIft

代码保护的模块

图1-1C28x功能框图

+器件上提供96个中断,45个可用;

+XINTF在F2810上不可用

1.2引脚分布及引脚功能

TMS320F2812芯片的封装方式为179引脚GHH球形网格阵列BGA(BallGridArray)封装和176引脚PGF低剖面四芯线扁平LQFP(Low-profileQuad)封装,其引脚分布分别

如图1-2(BGA封装底视图)和图1-3(LQFP封装顶视图)所示。

TMS320F2810芯片的封装方式为128引脚PBKLQFP封装,其引脚分布情况如图1-4(顶视图)所示。

1-2详细描述了芯片

F2810和F2812的引脚功能及信号情况。

所有输入引脚的电平

均与

TTL兼容;

所有引脚的输出均为3.3VCMOS电平;

输入不能承受5V电压;

上拉电

流/下拉电流均为100卩

所有引脚的输出缓冲器驱动能力(有输出功能的)典型值是4mA

5wiKhii”rAui

rvimin

l>

K}

v”「

IAl弩

ijFPIJ

MW

XR^'

机港

)E$T1

Mir.

FV^TJlS

Cxpa.史週

Z亀1已

7F<

ri

6^hy

制纽

PUMl1

X~~\

KDPl

{'

5TFICP

QwlinLWk

町苛甲

'

■1_BlMF

ivw

咏曲、HIMU

xow

c

Va1

jM)IWrTii

亦切r

聲Trx^fs

VH.n-J

KD[iI]

WT.I

亦T¥

人

r沁釈

h1“

即何

IXJ

J

III1

puw

11MR0

NLHI^J

gminj

(9

FN7*

Kon*

HIKI*JB

敕L•小

切*DA

KW!

(”11j

@

Cj

T.imn

TicMr

w;

rJpwM

Jjaw

■

:

X

MEIXRJk

Rllj

MlF^XAXlJ|J|

(

itA^r皿吋

fAP冷

Wnv.i

幼h)j

JXAR

()

r^tirtip-

XXIF帯

■1.'

打肛KT

Qj

XCl.Ktji'

l

Aviir%

加si

髦朋m-.iM’心工备昭

MW.

j*"

s.

ITwCE

XNAfll-XIMlJ

*UllO

fiTRi?

、_l<

心12

X'

fc—

細

S—

XIVT1

JMJC5OI,^1——r*

M^FiMio

tMlM

収丽ADCrKBO

Mxih^-i

■stnxnA

EMLI

(J

咖1怜串:

4CM1o

心心叭肿

Qy

JUIT

10(1^1

時(KFKW

咻TWW.J

Kmi*)

I-H

vM1M

JKLim

心11

TtLKH

itsrA

亦吋

(YkiV

i:

tckx

l'

™s'

Xi_式

1TD('

■jiwr

10

图1-2179引脚BGA封装底视图

M4fflwp8a

liTdk

虽・z「Mk・*

£

_・刁4|器»

=jrri-nuH-&

M«

rri!

帝

圭圭Es圭E圭z=丰圭圭亠〒

图1-3176引脚LQFP封装顶视图

t订g*斗

——i;

丿

I■"

httupr^wwir

I」、H4P2

t■»

FUrw^PCFT^TP

,■■X:

TU'

IJCIN

=<

F乍

I■

*tB7W1

气『*】》旳:

話』

Alll^Ai€^l=ADLjhJUt*-I

Ttmtrj■

Til

■ffHU*—■

“JiHiLbEd■-

^-..■■■~

.I'

U'

HlkllAri=T

I1■Mh»

\J*I|

MKfflV=■

!

Jt

Jlhr/hh

<

d«

E

苇二£

ssb-J

3.UJUS-■Fws5JU.S5>

33

XLr™m专.-£

3-f$dj-run>

KI*-W3£

EU9ms匕却ESUJOy:

ruJr・-m-#*A

图1-4128引脚PBK封装顶视图

表1-2引脚功能和信号情况?

引脚号

名字

179针

GHH

176针

PGF

128针

I/O/Z

PU/PDS

说

明

XINTF信号(只限于F2812)

XA[18]

D7

158

—

0/Z

XA[17]

B7

156

XA[16]

A8

152

O/Z

XA[15]

B9

148

XA[14]

A10

144

XA[13]

E10

141

XA[12]

C11

138

XA[11]

A14

132

XA[10]

C12

130

XA[9]

D14

125

XA[8]

E12

XA[7]

F12

121

XA[6]

G14

111

19位地址总线

XA[5]

H13

108

XA[4]

J12

103

XA[3]

M11

85

XA[2]

N10

80

XA[1]

M2

43

XA[0]

G5

18

XD[15]

A9

147

PU

XD[14]

B11

139

XD[13]

J10

97

XD[12]

L14

96

XD[11]

N9

74

XD[10]

L9

73

XD[9]

M8

68

XD[8]

P7

65

16位数据总线

L5

54

XD[7]

XD[6]

L3

39

XD[5]

J5

36

——

XD[4]

K3

XD[3]

J3

30

XD[2]

H5

27

XD[1]

H3

24

XD[0]

G3

21

PU/PD

S

说明

176针PGF

PBK封装

XINTF信号(仅F2812)

可选择微处理器/微计算机模式。

可以在两者之间切换。

为高电平时外部接口上的区域7有效,为低电平时区域7无效,可使

XMP/MC

F1

17

I

用片的BootROM功能。

复位时该信号被锁存在XINTCNF2寄存器中,通过软件可以修改这种模式的状态。

此信号是异步输

入,并与XTIMCLK同步

外部DMA保持请求信号。

XHOLD为低

E7

159

电平时请求XINTF释放外部总线,并把所

有的总线与选通端置为高阻态。

当对总线

XHOLD

的操作完成且没有即将对XINTF进行访

问时,XINTF释放总线。

此信号是异步输入并与XTIMCLK同步

K10

82

外部DMA保持确认信号。

当XINTF响应

XHOLD的请求时XHOLDA呈低电平,所

XHOLDA

有的XINTF总线和选通端呈高阻态。

XHOLD和XHOLDA信号同时发出。

当

XHOLDA有效(低)时外部器件只能使用外部总线

XZCSOAN

QD1

P1

44

XINTF区域0和区域1的片选,当访问

XINTF区域0或1时有效(低)

XZCS2

P13

88

XINTF区域2的片选。

当访问XINTF区域

2时有效(低)

XZCS6AN

QD7

B13

133

XINTF区域6和7的片选。

当访问区域6或7时有效(低)

XWE

N11

84

写有效。

有效时为低电平。

写选通信号是每个区域操作的基础,由XTIMINGx寄存

器的前一周期、当前周期和后一周期的值确定

XRD

M3

42

读有效。

低电平读选通。

读选通信号是每个区域操作的基础,由XTIMINGx]寄存器的前一周期、当前周期和后一周期的值确定。

注意:

XRD和XWE是互斥信号

XR/W

N4

51

通常为高电平,当为低电平时表示处于写周期,当为高电平时表示处于读周期

XREADY

B6

161

数据准备输入,被置1表示外设已为访问做好准备。

XREADY可被设置为同步或异步输入。

在同步模式中,XINTF接口块在当前周期结束之前的一个

XTIMCLK时钟周期要求XREADY有效。

在异步模式中,在当前的周期结束前XINTF接口块以

XTIMCLK的周期作为周期对XREADY采样3次。

以XTIMCLK频率对XREADY的采样与

XCLKOUT的模式无关

JTAG和其他信号

振荡器输入/部振荡器输入,该引脚也可以用来提供

X1/XCLKI

N

K9

77

58

外部时钟。

28x能够使用一个外部时钟源,条件是要在该引脚上提供适当的驱动电平,—为了适应1.8V核数字电源(Vdd),而不是3.3V的I/O电源(Vddio)。

可以使用一个嵌位二极管去嵌位时钟信号,以保证它的逻辑高电平不超过Vdd(1.8V或1.9V)或者去

使用一个1.8V的振荡器

X2

M9

76

57

振荡器输出

源于SYSCLKOUT的单个时钟输出,用来产生片和]

XCLKOU

F11

119

87

片外等待状态,作为通用时钟源。

XCLKOUT与

T

SYSCLKOUT的频率或者相等,或是它的1/2,或

是1/4。

复位时XCLKOUT=SYSCLKOUT/4

TESTSEL

A13

134

PD

测试引脚,为TI保留,必须接地

Xrs

D6

160

113

I/O

器件复位(输入)及看门狗复位(输岀)。

器件复

位,XRS使器件终止运行,PC指向地址0x3FFFC0

(注:

0xXXXXXX中的0x指出后面的数是十六进制数。

例如0x3FFFC0=3FFFC0h)当XRS为高电平时,程序从PC所指岀的位置开始运行。

当看门狗产生复位时,DSP将该引脚驱动为低电平,在看门狗复位期间,低电平将持续512个XCLKIN周期。

该引脚的输岀缓冲器是一个带有部上拉(典型值

100mA)的开漏缓冲器,推荐该引脚应该由一个开漏设备去驱动

TEST1

M7

67

测试引脚,为TI保留,必须悬空

TEST2

N7

66

50

续表

PGF封装

TRST

B12

135

98

有部上拉的JTAG测试复位。

当它为高电平时扫描系统控制器件的操作。

若信号悬空或为低电平,器件以功能模式操作,测试复位信号被忽略

在TRST上不要用上拉电阻。

它部

有上拉部件。

在强噪声的环境中需要使用

附加上拉电阻,此电阻值根据调试器设计

的驱动能力而定。

一般取22kQ即能提供足够的保护。

因为有了这种应用特性,所以使得调试器和应用目标板都有合适且有效的操作

TCK

A12

136

99

JTAG测试时钟,带有部上拉功能

TMS

D13

126

92

JTAG测试模式选择端,有部上拉功能,在TCK的上升沿TAP控制器计数一系列的控制输入

带上拉功能的JTAG测试数据输入端。

在

TDI

C13

131

TCK的上升沿,TDI被锁存到选择寄存器、、]

指令寄存器或数据寄存器中

TDO

D12

127

93

JTAG扫描输出,测试数据输出。

在TCK

的下降沿将选择寄存器的容从TDO移出

EMU0

D11

137

100

带上拉功能的仿真器I/O口引脚0,当

TGST为高电平时,此引脚用作中断输入。

该中断来自仿真系统,并通过JTAG扫描

定义为输入/输岀

EMU1

C9

146

105

仿真器引脚1,当TGST为高电平时,此引脚输出无效,用作中断输入。

该中断来自仿真系统的输入,通过JTAG扫描定义为输入/输出

ADC模拟输入信号

ADCINA7

B5

167

ADCINA6

D5

168

120

ADCINA5

E5

169

ADCINA4

A4

170

122

采样/保持A的8通道模拟输入。

在器件未

ADCINA3

B4

171

123

上电之前ADC引脚不会被驱动

ADCINA2

C4

172

124

ADCINA1

D4

173

ADCINA0

A3

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- TMS320C28x 系列 DSP 芯片 结构 引脚 功能

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

建筑工程编制依据及概况.docx

建筑工程编制依据及概况.docx