数电实验报告 实验二利用MSI设计组合逻辑电路.docx

数电实验报告 实验二利用MSI设计组合逻辑电路.docx

- 文档编号:744875

- 上传时间:2023-04-30

- 格式:DOCX

- 页数:31

- 大小:1.79MB

数电实验报告 实验二利用MSI设计组合逻辑电路.docx

《数电实验报告 实验二利用MSI设计组合逻辑电路.docx》由会员分享,可在线阅读,更多相关《数电实验报告 实验二利用MSI设计组合逻辑电路.docx(31页珍藏版)》请在冰点文库上搜索。

数电实验报告实验二利用MSI设计组合逻辑电路

实验二利用MSI设计组合逻辑电路

【实验目的】

1.熟悉编码器、译码器、数据选择器等组合逻辑功能模块的功能和使用方法

2.掌握用MSI设计的组合逻辑电路方法

【实验仪器】

1.数字电路实验箱、数字万用表、示波器

2.虚拟器件:

74LS00、74LS197、74LS138、74LS15174LS7374LS86

【实验设计与分析】

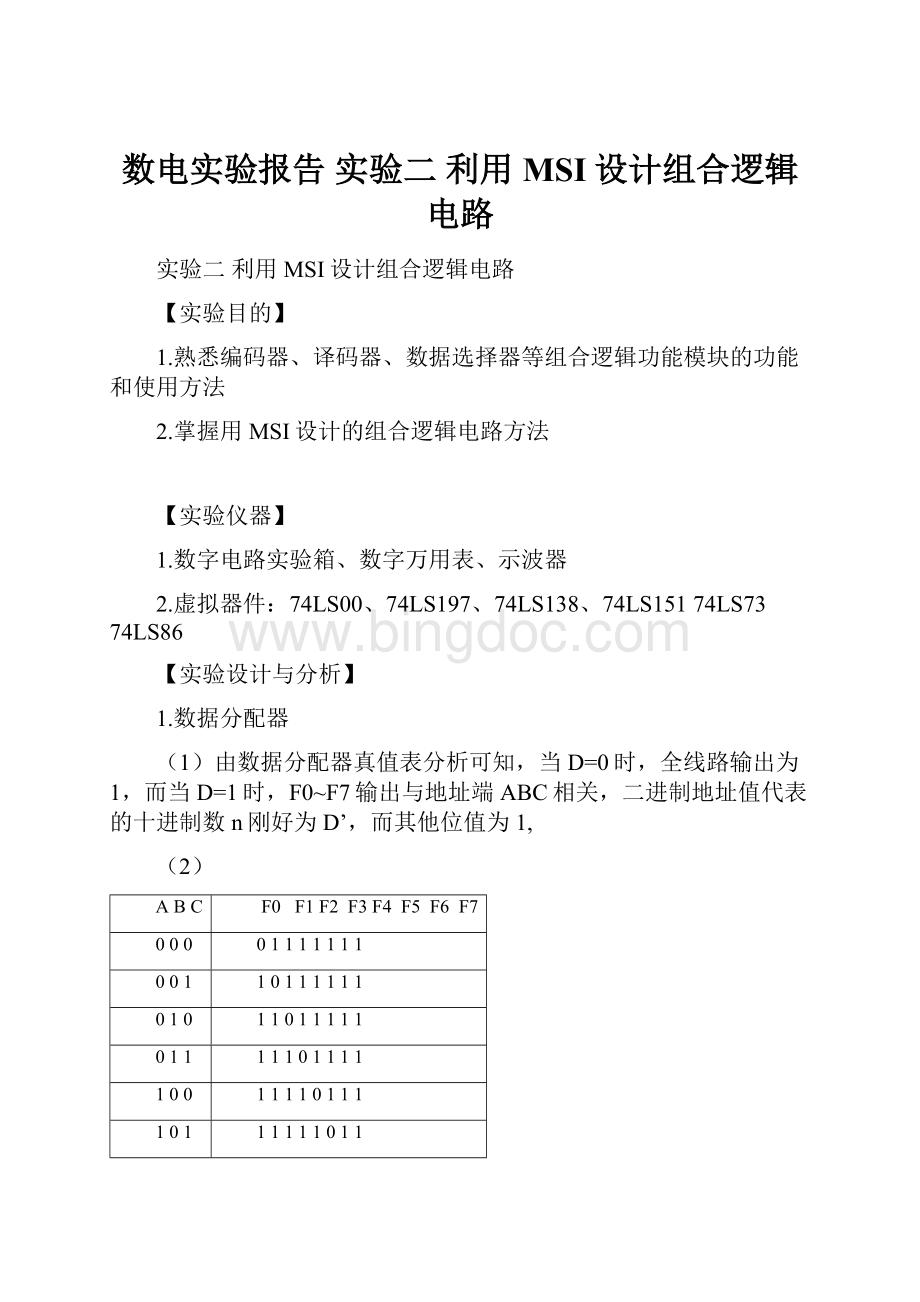

1.数据分配器

(1)由数据分配器真值表分析可知,当D=0时,全线路输出为1,而当D=1时,F0~F7输出与地址端ABC相关,二进制地址值代表的十进制数n刚好为D’,而其他位值为1,

(2)

ABC

F0F1F2F3F4F5F6F7

000

01111111

001

10111111

010

11011111

011

11101111

100

11110111

101

11111011

110

11111101

111

11111110

F0卡诺图:

A\BC

00

01

11

10

0

0

1

1

1

1

1

1

1

1

卡诺图化简,得

F0’=A’B’C’

即

F0=(A’B’C’)’

同理

F1=(A’B’C)’

F2=(A’BC’)’

F3=(A’BC)’

F4=(AB’C’)’

F5=(AB’C)’

F6=(ABC’)’

F7=(ABC)’

分析3线-8线译码器特点,当GS不同值时,有以下真值表

Gs=0

S2S1S0

Y0’Y1’Y2’Y3’Y4’Y5’Y6’Y7’

000

11111111

001

11111111

010

11111111

011

11111111

100

11111111

101

11111111

110

11111111

111

11111111

Gs=1

000

01111111

001

10111111

010

11011111

011

11101111

100

11110111

101

11111011

110

11111101

111

11111110

Y0’的卡诺图

GsS2\’S1S0

00

01

11

10

00

1

1

1

1

01

1

1

1

1

11

1

1

1

10

0

1

1

1

YO=GsS2’S1’S0’

即

Y0’=(Gs’S2’S1’S0’)’

同理

Y1’=(Gs’S2’S1’S0)’

Y2’=(Gs’S2’S1S0’)’

Y3’=(Gs’S2’S1S0)’

Y4’=(Gs’S2S1’S0’)’

Y5’=(Gs’S2S1’S0)’

Y6’=(Gs’S2S1S0’)’

Y7’=(Gs’S2S1S0)’

显然当Gs=1时,Y’=F

(3)对比

(2)中不同Gs条件下译码器和数据分配器的真值表可以发现,当另Gs’与数据输入D信号一致,S2~S0作为地址段输入的ABC,两者真值表一致,即使译码器变成了数据分配器。

Gs输入端有3端,令G1为数据D输入,其他两端接低电平。

(4)电路设计

(5)仿真波形

2.LU(LogicUnit逻辑单元)设计

(1)分析LU功能,得出如下真值表

S1S0

AB

Y

00

00

00

00

00

01

10

11

0

0

0

1

01

01

01

01

00

01

10

11

0

1

1

1

10

10

10

10

00

01

10

11

1

0

0

1

11

11

11

11

00

01

10

11

1

1

0

0

利用74LS151实现数据选择,那么无需计算逻辑表达式,无需卡诺图化简

(2)16行真值化简为8行真值

若用2组74LS151,可联合成16路输出,

若只用1组74LS151,则需要把Y的值与其中一个输入变量联合起来

观察S1与Y的关系

S1=0

S1=1

X0

Y0=0

Y8=1

X1

Y1=0

Y9=0

X2

Y2=0

Y10=0

X3

Y3=1

Y11=1

X4

Y4=0

Y12=1

X5

Y5=1

Y13=1

X6

Y6=1

Y14=0

X7

Y7=1

Y15=0

可知X1X2X3X5与S1无关

X0=X4=S1X6=X7=S1’

故简化成了设计

(3)根据

(1)&

(2)的真值表分析,可以发现有4组输入变量,1组输出变量,其中s1通过把数据输入端的值与S1关联而简化,故利用3组变量实现了16组输出结果。

另外利用74LS197实现16进制4组变量的输入

(4)电路设计

(5)波形

3.AU(ArithmeticUnit算术单元)设计

(1)分析AU功能,得出如下真值表格

S

A

B

D

Cn

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

0

0

1

0

1

1

1

1

1

0

1

0

1

1

1

0

0

(2)

a.通过卡诺图化简只使用门电路

卡诺图-D

S\AB

00

01

11

10

0

0

1

0

1

1

0

1

0

1

化简显然D=A’B+AB’=A⊕B

卡诺图-Cn

S\AB

00

01

11

10

0

0

0

1

0

1

0

1

0

0

显然Cn=S’AB+SA’B

b.使用74LS138元件

分析真值表,利用最小项目之和,即真值为1的所有项之和,不必使用卡诺图,得到表达式

D列真值为1的有第1256项

D=(M1’+M2’+M5’+M6’)’

Cn列真值为1的有第35项

Cn=(m3’+m5’)’

利用译码器输出特点,用译码器输出最小项的反以及利用与非的通用特性实现最小项之和的表达式,而可以吧S、A、B作为地址段信号输入

(3)根据3输入二输出的数据特点,可以利用74LS138和2个74LS20,输出

(2)中分析得到的两项表达式D、Cn

C.使用74LS151元件

(4)电路设计

(5)波形分析

4.ALU设计

(1)分析ALU功能

从输入上看,分别有6输入,其中S2`S0为地址分配值,ABCn都是参与算术运算的变量。

基于整个电路共有23=8种算术功能,基于数据选择器的功能,设计8个对应的子电路接入。

以下是真值表

S2

S1

S0

A

B

Cn

Y

Y'

0

0

0

0

0

0

0

1

0

0

0

0

0

1

0

1

0

0

0

0

1

0

1

0

0

0

0

0

1

1

1

0

0

0

0

1

0

0

1

0

0

0

0

1

0

1

1

0

0

0

0

1

1

0

1

0

0

0

0

1

1

1

1

0

0

0

1

0

0

0

0

1

0

0

1

0

0

1

0

1

0

0

1

0

1

0

1

0

0

0

1

0

1

1

1

0

0

0

1

1

0

0

1

0

0

0

1

1

0

1

1

0

0

0

1

1

1

0

1

0

0

0

1

1

1

1

1

0

0

1

0

0

0

0

1

0

0

1

0

0

0

1

1

0

0

1

0

0

1

0

1

0

0

1

0

0

1

1

1

0

0

1

0

1

0

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

0

0

1

0

1

0

1

1

1

0

1

0

1

1

0

0

0

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

0

1

0

1

1

0

1

1

0

1

0

1

1

1

0

0

1

0

0

1

1

1

0

1

1

0

0

1

1

1

1

0

0

1

0

1

1

1

1

1

0

1

1

0

0

0

0

0

0

1

1

0

0

0

0

1

0

1

1

0

0

0

1

0

1

0

1

0

0

0

1

1

1

0

1

0

0

1

0

0

1

0

1

0

0

1

0

1

1

0

1

0

0

1

1

0

0

1

1

0

0

1

1

1

0

1

1

0

1

0

0

0

0

0

1

0

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

0

1

1

0

1

1

0

0

1

0

1

0

1

1

0

1

0

1

1

0

1

1

1

0

0

1

1

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

1

1

0

0

0

1

1

1

1

1

0

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

0

1

0

0

1

0

1

1

0

1

0

1

0

0

1

1

0

1

1

0

0

0

1

1

0

1

1

1

1

1

1

1

1

0

0

0

0

0

1

1

1

0

0

1

0

0

1

1

1

0

1

0

0

0

1

1

1

0

1

1

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

1

0

0

1

1

1

1

1

0

0

0

1

1

1

1

1

1

0

0

(2)真值表分析

按照8项算术功能,我们分成8组真值表来分析。

第0~7行:

实现与运算,即A.B

第8~15行:

实现或运算,即A+B

第16~23行:

实现取反A’

第24~31行:

实现取反B’

第32~39行:

实现异或A⊕B

第40~47行:

实现全加,子真值表

A

B

Cn

Y

Y’

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

对于Y得卡诺图

C\AB

0

1

11

10

0

0

1

0

1

1

1

0

1

0

显然Y=A’BC’+AB’C’+A’B’C+ABC无法化简

但是根据进位原理可以看到Y的输出和ABC进行异或运算的结果一致,因此采取异或运算A⊕B⊕C

而Y’实际代表的输出是ABCn运算得到的进位。

同AU的设计思路,利用74LS138我们把真值为1的所有最小项累加(即m3m5m6m7)利用或运算即可得到结果,即。

Y’=M3+M5+M6+m7

第48~55行:

A

B

Cn

Y

Y

0

0

0

0

0

0

0

1

1

1

0

1

0

1

1

0

1

1

0

1

1

0

0

1

0

1

0

1

0

0

1

1

0

0

0

1

1

1

1

1

对于Y得卡诺图

C\AB

0

1

11

10

0

0

1

0

1

1

1

0

1

0

显然Y=A’BC’+AB’C’+A’B’C+ABC无法化简

但是根据进位原理可以看到Y的输出和ABC进行异或运算的结果一致,因此采取异或运算A⊕B⊕C

而Y’实际代表的输出是ABCn运算得到的借位。

同AU的设计思路,利用74LS138我们把真值为1的所有最小项累加(即m1m2m3m7)利用或运算即可得到结果,即。

Y’=M1+M2+M3+m7

第56~63行:

最后是清零运算

即Y=Y’=0

(3)电路子功能设计

a.电路需要6路信号,可以采用2组74LS197联合,8路取其6即可实现。

但是由于实验室器材限制,只有1个74LS197元件,因此可以采用74LS73J-K触发器,从74ls197的q3输出端接入,实现串联,即可得到六十四进制6路信号输出

b电路一共有两路输出,由于有8项子功能电路,采用74LS151数据选择器,按照s2~s0地址值输出对应电路运算结果。

但是由于元件有限,因此把2组输出分开2次实验进行输出,第一次输出逻辑运算的结果以及算术运算的位运算结果。

第二次输出所有逻辑运算结果的反,以及算术运算的进位、借位结果。

c

与运算:

使用2组与非74LS00

或运算:

使用3个与非门74LS00等效或门运算(没有或运算元件可用)

反相运算:

使用与非门即可,由于在实现或运算已经对信号进行过反相,因此复用或运算的电路即可

异或:

可使用二门输入异或74LS86实现

全加:

位运算根据真值表分析,使用异或运算即可,可使用2个二门输入异或实现3门输入异或运算

进位运算参考AU设计的半加器设计,使用74LS138和四门输入与非即可

全减法:

位运算根据真值表分析,使用异或运算即可,可使用2个二门输入异或实现3门输入异或运算

借位运算参考AU设计的半减器设计,使用74LS138和四门输入与非即可

清零:

根据两个不同输出端(Y\Y’),分别接入地电平或者高电平即可。

(4)电路设计图

(5)仿真波形

【实验结果及其分析】

1.数据分配器

(1).波形记录

(2).实验结论

根据接线关系,可知

D0-----C

D1-----B

D2-----A

D3-----D

D8-----F0

D9-----F1

D10-----F2

D11-----F3

D12-----F4

D13-----F5

D14-----F6

D15-----F7

D16-----F8

根据波形绘制真值表

D=0

ABC

F0F1F2F3F4F5F6F7

000

11111111

001

11111111

010

11111111

011

11111111

100

11111111

101

11111111

110

11111111

111

11111111

D=1

000

01111111

001

10111111

010

11011111

011

11101111

100

11110111

101

11111011

110

11111101

111

11111110

通过与预习时的实验分析所得的真值表可知,实验结果符合预期,实现了数据分配功能。

(3)问题记录

a.预习分析时接口输入是ABC顺序,实验也是,但是从逻辑上应该是CBA顺序,虽然影响不大,不过波形顺序变成了CBAD,而不是ABCD有点影响分析。

b.忘记记录cp0波形

2.LU(LogicUnit逻辑单元)设计

(1)波形记录

(2)实验结论

根据接线关系,可知

D0-----B

D1-----A

D2-----S0

D3-----S1

D7-----Y

根据波形绘制真值表

S0S1

AB

Y

00

00

00

00

00

01

10

11

0

0

0

1

01

01

01

01

00

01

10

11

0

1

1

1

10

10

10

10

00

01

10

11

1

0

0

1

11

11

11

11

00

01

10

11

1

1

0

0

符合预习时实验分析所得的真值表,故认为改组合电路实现了基本的LU功能

(3)问题记录

a.忘记实验时只有1个74ls151,也没有留意老师说的把4变量输入变成3变量输入,因此在预习时设计是由2个74LS151设计成的16路输出电路。

当天实验时才匆匆忙忙修改电路。

b.起初实验波形与预习波形不一致,以为电路接线有误,后来与预习绘制的真值表对比发现实验波形是正确的,但是实验的电路是错的,说明预习的时候没有对预习所得的仿真波形检验和分析

c根据b的问题,实验后分析结果,原因在于,74LS197的四路输出Q0~Q3其中的三路Q0Q1Q2原本对应于输入CBA但是接线次序错误,变成ABC,即反了,所以按照输出波形的时序来看,输出波形是错误的,但是74LS151的8个数据段连接是没错的,经过改正ABC的地址段接线后,波形正确。

3.AU

(1)实验波形记录

(2)实验结论

根据接线关系,

D0-----输出(A+B/A-B)

D1-----Cn(进/借位)

D11-----S

D10-----A

D9-----B

根据波形(时序图)绘制真值表,有

S

A

B

D

Cn

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

0

0

1

0

1

1

1

1

1

0

1

0

1

1

1

0

0

分析,真值表可知道,与实验设计时所得的真值表一致(即波形一致),实现了半加半减的算术功能,即A+B\A-B以及对应进位借位结果。

(3)问题记录

a.起初实验时,没有预先检查确认74LS138接口顺序,接的时候刚好反了,因此波形和仿真实验时差异较大(错误的波形忘记记录了),

b.波形一样,所以只放了一张波形记录图。

4.ALU

(1)实验波形记录

(2)实验结论

第一组

D0-----Y

D11-----S2

D12-----S1

D13-----S0

D14-----A

D15-----B

D16-----C

第二组

D0-----Y’

D11-----S2

D12-----S1

D13-----S0

D14-----A

D15-----B

D16-----C

根据波形(时序图)绘制真值表,有

S2

S1

S0

A

B

C

Y

Y'

0

0

0

0

0

0

0

1

0

0

0

0

0

1

0

1

0

0

0

0

1

0

1

0

0

0

0

0

1

1

1

0

0

0

0

1

0

0

1

0

0

0

0

1

0

1

1

0

0

0

0

1

1

0

1

0

0

0

0

1

1

1

1

0

0

0

1

0

0

0

0

1

0

0

1

0

0

1

0

1

0

0

1

0

1

0

1

0

0

0

1

0

1

1

1

0

0

0

1

1

0

0

1

0

0

0

1

1

0

1

1

0

0

0

1

1

1

0

1

0

0

0

1

1

1

1

1

0

0

1

0

0

0

0

1

0

0

1

0

0

0

1

1

0

0

1

0

0

1

0

1

0

0

1

0

0

1

1

1

0

0

1

0

1

0

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

0

0

1

0

1

0

1

1

1

0

1

0

1

1

0

0

0

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

0

1

0

1

1

0

1

1

0

1

0

1

1

1

0

0

1

0

0

1

1

1

0

1

1

0

0

1

1

1

1

0

0

1

0

1

1

1

1

1

0

1

1

0

0

0

0

0

0

1

1

0

0

0

0

1

0

1

1

0

0

0

1

0

1

0

1

0

0

0

1

1

1

0

1

0

0

1

0

0

1

0

1

0

0

1

0

1

1

0

1

0

0

1

1

0

0

1

1

0

0

1

1

1

0

1

1

0

1

0

0

0

0

0

1

0

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

0

1

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数电实验报告 实验二 利用MSI设计组合逻辑电路 实验 报告 利用 MSI 设计 组合 逻辑电路

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

整编新型生态农业旅游休闲农庄项目发展建设市场研究报告.docx

整编新型生态农业旅游休闲农庄项目发展建设市场研究报告.docx

CE培训教材ppt.ppt

CE培训教材ppt.ppt