Verilog HDL 6位数码管扫描驱动汇总Word下载.docx

Verilog HDL 6位数码管扫描驱动汇总Word下载.docx

- 文档编号:607509

- 上传时间:2023-04-29

- 格式:DOCX

- 页数:11

- 大小:15.84KB

Verilog HDL 6位数码管扫描驱动汇总Word下载.docx

《Verilog HDL 6位数码管扫描驱动汇总Word下载.docx》由会员分享,可在线阅读,更多相关《Verilog HDL 6位数码管扫描驱动汇总Word下载.docx(11页珍藏版)》请在冰点文库上搜索。

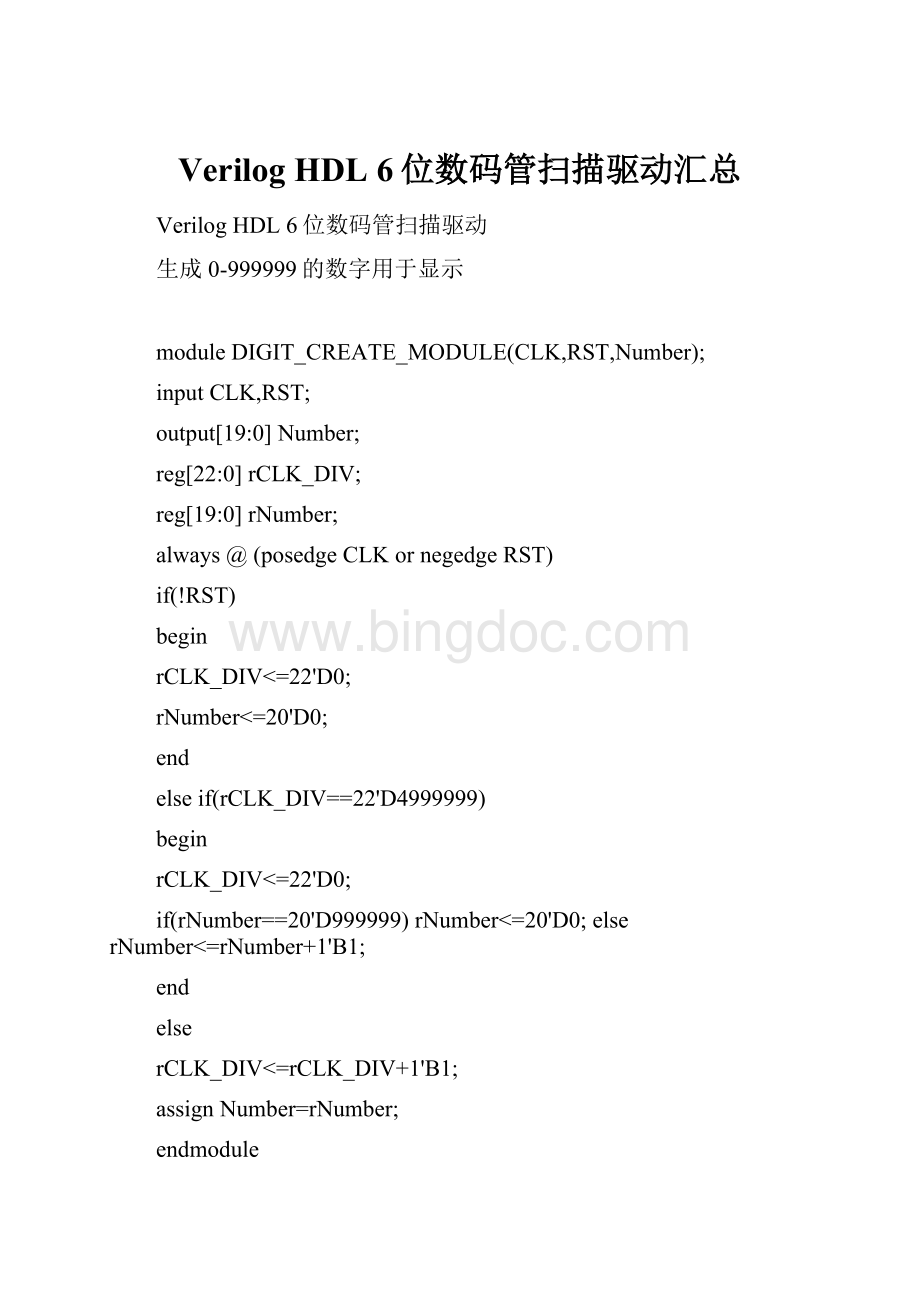

elserNumber<

=rNumber+1'

B1;

else

=rCLK_DIV+1'

assignNumber=rNumber;

endmodule

数码管驱动

moduleDIGIT_MODULE(CLK,RST,DIG,SEL,BCD0,BCD1,BCD2,BCD3,BCD4,BCD5);

output[7:

0]DIG;

output[5:

0]SEL;

input[3:

0]BCD0,BCD1,BCD2,BCD3,BCD4,BCD5;

parameterN0=8'

B11000000,N1=8'

b11111001,N2=8'

b10100100,N3=8'

b10110000,N4=8'

b10011001,

N5=8'

B10010010,N6=8'

b10000010,N7=8'

b11111000,N8=8'

b10000000,N9=8'

b10010000;

reg[7:

0]rD0,rD1,rD2,rD3,rD4,rD5;

rD0<

=N0;

rD1<

rD2<

rD3<

rD4<

rD5<

case(BCD0)

4'

D0:

rD0<

D1:

=N1;

D2:

=N2;

D3:

=N3;

D4:

=N4;

D5:

=N5;

D6:

=N6;

D7:

=N7;

D8:

=N8;

D9:

=N9;

default:

endcase;

case(BCD1)

rD1<

case(BCD2)

rD2<

case(BCD3)

rD3<

case(BCD4)

rD4<

case(BCD5)

rD5<

reg[11:

always@(negedgeCLKornegedgeRST)

=12'

elseif(rCLK_DIV==12'

D3599)

reg[5:

0]rSEL;

0]rDIG;

rSEL<

=6'

B111111;

rDIG<

D0)

B111110;

=rD5;

D600)

B111101;

=rD4;

D1200)

B111011;

=rD3;

D1800)

B110111;

=rD2;

D2400)

B101111;

=rD1;

D3000)

B011111;

=rD0;

assignDIG=rDIG;

assignSEL=rSEL;

20bit二进制转BCD码

moduleBIN_TO_BCD_MODULE(BIN,BCD0,BCD1,BCD2,BCD3,BCD4,BCD5);

parameterBIT_WIDTH=20;

input[BIT_WIDTH-1:

0]BIN;

output[3:

function[3:

0]LSA3;

input[3:

0]IN;

case(IN)

B0000:

LSA3=4'

B0000;

B0001:

B0001;

B0010:

B0010;

B0011:

B0011;

B0100:

B0100;

B0101:

B1000;

B0110:

B1001;

B0111:

B1010;

B1000:

B1011;

B1001:

B1100;

endcase

endfunction

wire[3:

0]wA[1:

BIT_WIDTH-3];

0]wB[1:

assignwA[1]={1'

B0,BIN[BIT_WIDTH-1:

BIT_WIDTH-3]};

assignwB[1]=LSA3(wA[1]);

genvargB;

generatefor(gB=2;

gB<

=BIT_WIDTH-3;

gB=gB+1)

begin:

CA

assignwA[gB]={wB[gB-1][2:

0],BIN[BIT_WIDTH-gB-2]};

assignwB[gB]=LSA3(wA[gB]);

endgenerate

0]wC[1:

BIT_WIDTH-6];

0]wD[1:

assignwC[1]={1'

B0,wB[1][3],wB[2][3],wB[3][3]};

assignwD[1]=LSA3(wC[1]);

genvargD;

generatefor(gD=2;

gD<

=BIT_WIDTH-6;

gD=gD+1)

CB

assignwC[gD]={wD[gD-1][2:

0],wB[gD+2][3]};

assignwD[gD]=LSA3(wC[gD]);

0]wE[1:

BIT_WIDTH-9];

0]wF[1:

assignwE[1]={1'

B0,wD[1][3],wD[2][3],wD[3][3]};

assignwF[1]=LSA3(wE[1]);

genvargF;

generatefor(gF=2;

gF<

=BIT_WIDTH-9;

gF=gF+1)

CC

assignwE[gF]={wF[gF-1][2:

0],wD[gF+2][3]};

assignwF[gF]=LSA3(wE[gF]);

0]wG[1:

BIT_WIDTH-12];

0]wH[1:

assignwG[1]={1'

B0,wF[1][3],wF[2][3],wF[3][3]};

assignwH[1]=LSA3(wG[1]);

genvargH;

generatefor(gH=2;

gH<

=BIT_WIDTH-12;

gH=gH+1)

CD

assignwG[gH]={wH[gH-1][2:

0],wF[gH+2][3]};

assignwH[gH]=LSA3(wG[gH]);

0]wI[1:

BIT_WIDTH-15];

0]wJ[1:

assignwI[1]={1'

B0,wH[1][3],wH[2][3],wH[3][3]};

assignwJ[1]=LSA3(wI[1]);

genvargJ;

generatefor(gJ=2;

gJ<

=BIT_WIDTH-15;

gJ=gJ+1)

CE

assignwI[gJ]={wJ[gJ-1][2:

0],wH[gJ+2][3]};

assignwJ[gJ]=LSA3(wI[gJ]);

0]wK[1:

BIT_WIDTH-18];

0]wL[1:

assignwK[1]={1'

B0,wJ[1][3],wJ[2][3],wJ[3][3]};

assignwL[1]=LSA3(wK[1]);

genvargL;

generatefor(gL=2;

gL<

=BIT_WIDTH-18;

gL=gL+1)

CF

assignwK[gL]={wL[gL-1][2:

0],wJ[gL+2][3]};

assignwL[gL]=LSA3(wK[gL]);

assignBCD0={wB[BIT_WIDTH-3][2:

0],BIN[0]};

assignBCD1={wD[BIT_WIDTH-6][2:

0],wB[BIT_WIDTH-3][3]};

assignBCD2={wF[BIT_WIDTH-9][2:

0],wD[BIT_WIDTH-6][3]};

assignBCD3={wH[BIT_WIDTH-12][2:

0],wF[BIT_WIDTH-9][3]};

assignBCD4={wJ[BIT_WIDTH-15][2:

0],wH[BIT_WIDTH-12][3]};

assignBCD5={wL[BIT_WIDTH-18][2:

0],wJ[BIT_WIDTH-15][3]};

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- Verilog HDL 6位数码管扫描驱动汇总 数码管 扫描 驱动 汇总

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

整编新型生态农业旅游休闲农庄项目发展建设市场研究报告.docx

整编新型生态农业旅游休闲农庄项目发展建设市场研究报告.docx