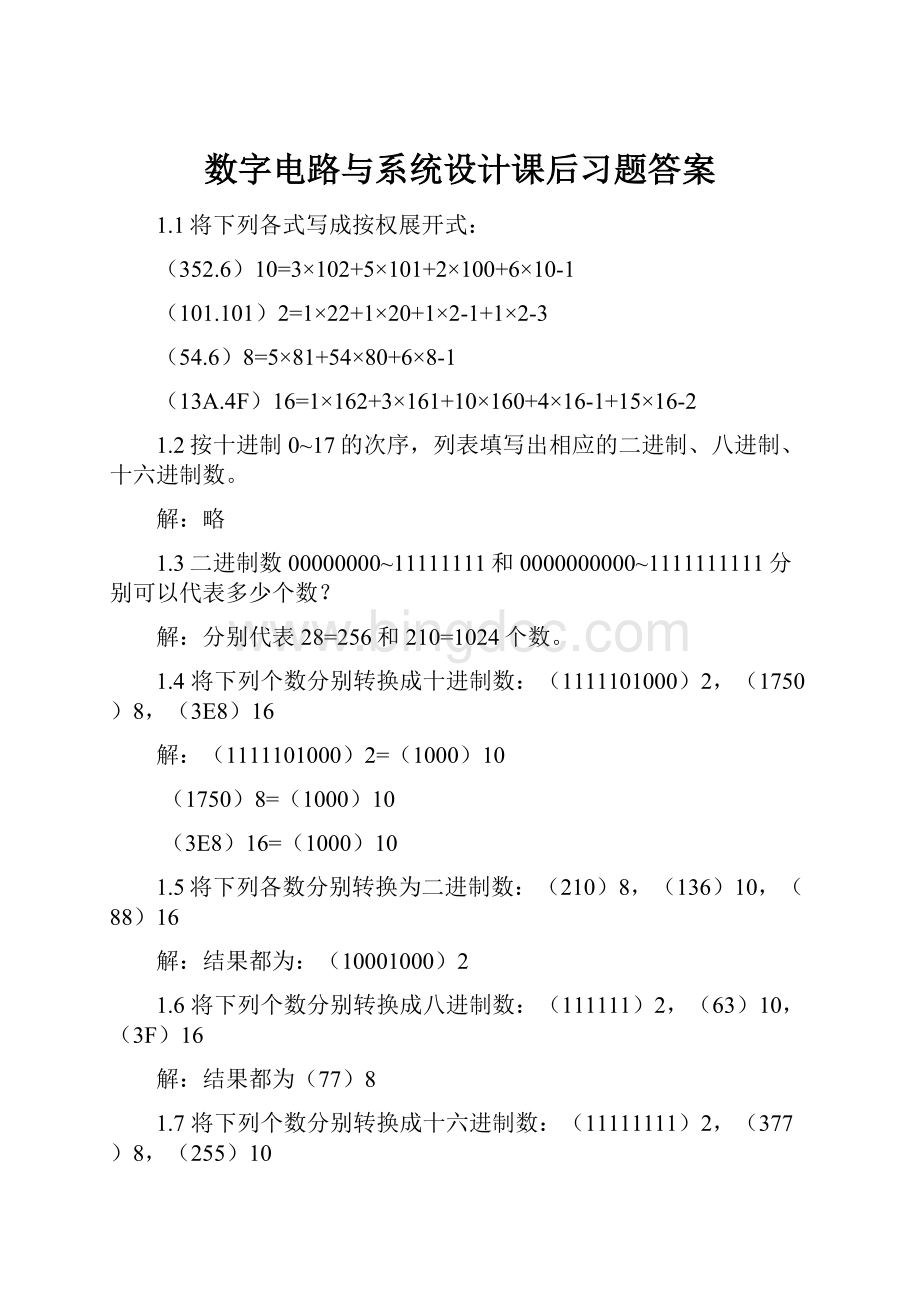

数字电路与系统设计课后习题答案Word文档下载推荐.docx

数字电路与系统设计课后习题答案Word文档下载推荐.docx

- 文档编号:1573192

- 上传时间:2023-05-01

- 格式:DOCX

- 页数:96

- 大小:848.27KB

数字电路与系统设计课后习题答案Word文档下载推荐.docx

《数字电路与系统设计课后习题答案Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《数字电路与系统设计课后习题答案Word文档下载推荐.docx(96页珍藏版)》请在冰点文库上搜索。

(0110.1010)余3循环BCD码=(1.1110)2

1.9用下列代码表示(123)10,(1011.01)2:

(1)8421BCD码:

(123)10=(000100100011)8421BCD

(1011.01)2=(11.25)10=(00010001.00100101)8421BCD

(2)余3BCD码

(123)10=(010001010110)余3BCD

(1011.01)2=(11.25)10=(01000100.01011000)余3BCD

1.10已知A=(1011010)2,B=(101111)2,C=(1010100)2,D=(110)2

(1)按二进制运算规律求A+B,A-B,C×

D,C÷

D,

(2)将A、B、C、D转换成十进制数后,求A+B,A-B,C×

D,并将结果与

(1)进行比较。

(1)A+B=(10001001)2=(137)10

A-B=(101011)2=(43)10

C×

D=(111111000)2=(504)10

C÷

D=(1110)2=(14)10

(2)A+B=(90)10+(47)10=(137)10

A-B=(90)10-(47)10=(43)10

D=(84)10×

(6)10=(504)10

D=(84)10÷

(6)10=(14)10

两种算法结果相同。

1.11试用8421BCD码完成下列十进制数的运算。

(1)5+8=(0101)8421BCD+(1000)8421BCD=1101+0110=(10110)8421BCD=13

(2)9+8=(1001)8421BCD+(1000)8421BCD=10001+0110=(10111)8421BCD=17

(3)58+27=(01011000)8421BCD+(00100111)8421BCD=01111111+0110=(10000101)8421BCD=85

(4)9-3=(1001)8421BCD-(0011)8421BCD=(0110)8421BCD=6

(5)87-25=(10000111)8421BCD-(00100101)8421BCD=(01100010)8421BCD=62

(6)843-348=(100001000011)8421BCD-(001101001000)8421BCD

=010011111011-01100110=(010010010101)8421BCD=495

1.12试导出1位余3BCD码加法运算的规则。

1位余3BCD码加法运算的规则

加法结果为合法余3BCD码或非法余3BCD码时,应对结果减3修正[即减(0011)2];

相加过程中,产生向高位的进位时,应对产生进位的代码进行“加33修正”[即加(00110011)2]。

2.1有A、B、C三个输入信号,试列出下列问题的真值表,并写出最小项表达式∑m()。

(1)如果A、B、C均为0或其中一个信号为1时。

输出F=1,其余情况下F=0。

(2)若A、B、C出现奇数个0时输出为1,其余情况输出为0。

(3)若A、B、C有两个或两个以上为1时,输出为1,其余情况下,输出为0。

F1(A,B,C)=∑m(0,1,2,4)

F2(A,B,C)=∑m(0,3,5,6)

F3(A,B,C)=∑m(3,5,6,7)

2.2试用真值表证明下列等式:

(1)AB+BC+AC=ABC+ABC

(2)AB+BC+AC=ABBCAC

证明:

(1)

ABC

AB+BC+AC

ABC+ABC

000

001

010

011

100

101

110

111

1

真值表相同,所以等式成立。

(2)略

2.3对下列函数,说明对输入变量的哪些取值组合其输出为1?

(1)F(A,B,C)=AB+BC+AC

(2)F(A,B,C)=(A+B+C)(A+B+C)

(3)F(A,B,C)=(AB+BC+AC)AC

本题可用真值表、化成最小项表达式、卡诺图等多种方法求解。

(1)F输出1的取值组合为:

011、101、110、111。

(2)F输出1的取值组合为:

001、010、011、100、101、110。

(3)F输出1的取值组合为:

101。

2.4试直接写出下列各式的反演式和对偶式。

(1)F(A,B,C,D,E)=[(AB+C)·

D+E]·

B

(2)F(A,B,C,D,E)=AB+CD+BC+D+CE+B+E

(3)F(A,B,C)=AB+CABC

(1)F=[(A+B)·

C+D]·

E+B

F'

=[(A+B)·

C+D]·

E+B

(2)F=(A+B)(C+D)·

(B+C)·

D·

(C+E)·

B·

E

=(A+B)(C+D)·

(B+C)·

D·

(C+E)·

B·

E

(3)F=(A+B)·

C+A+B+C

=(A+B)·

C+A+B+C

2.5用公式证明下列等式:

(1)AC+AB+BC+ACD=A+BC

(2)AB+AC+(B+C)D=AB+AC+D

(3)BCD+BCD+ACD+ABCD+ABCD+BCD+BCD=BC+BC+BD

(4)ABC+BC+BCD+ABD=A+B+C+D

2.6已知ab+ab=ab,ab+ab=ab,证明:

(1)abc=abc

(2)abc=abc

2.7试证明:

(1)若ab+ab=0则ax+by=ax+by

(2)若ab+ab=c,则ac+ac=b

2.8将下列函数展开成最小项之和:

(1)F(ABC)=A+BC

(2)F(ABCD)=(B+C)D+(A+B)C

(3)F(ABC)=A+B+C+A+B+C

(1)F(ABC)=∑m(3,4,5,6)

(2)F(ABCD)=∑m(1,3,5,6,7,9,13,14,15)

(3)F(ABC)=∑m(0,2,6)

2.9将题2.8中各题写成最大项表达式,并将结果与2.8题结果进行比较。

(1)F(ABC)=∏M(0,1,2)

(2)F(ABCD)=∏M(2,4,8,10,11,12)

(3)F(ABC)=∏M(1,3,4,5,7)

2.10试写出下列各函数表达式F的F和F的最小项表达式。

(1)F=ABCD+ACD+BCD

(2)F=AB+AB+BC

(1)F=∑m(0,1,2,3,5,6,7,8,9,10,13,14)

=∑m(1,2,5,6,7,8,9,10,12,13,14,15)

(2)F=∑m(0,1,2,3,12,13)

=∑m(2,3,12,13,14,15)

2.11试用公式法把下列各表达式化简为最简与或式

(1)F=A+ABC+ABC+BC+B

F=A+B

(2)F=(A+B)(A+B+C)(A+C)(B+C+D)

F'

=AB+AC

(3)F=AB+ABBC+BC

F=AB+BC+AC

或:

F=AB+AC+BC

(4)F=ACD+BC+BD+AB+AC+BC

F=AD+C+B

(5)F=AC+BC+B(AC+AC)

F=AC+BC

2.12用卡诺图把下列函数化简为最简与或式

(1)F(A,B,C)=m(0,1,2,4,5,7)

F=B+AC+AC

图略

(2)F(A,B,C,D)=m(0,2,5,6,7,9,10,14,15)

F=ABCD+ABD+ABD+BC+CD

(3)F(A,B,C,D)=m(0,1,4,7,9,10,13)+(2,5,8,12,15)

F=C+BD+BD

(4)F(A,B,C,D)=m(7,13,15)且ABC=0,ABC=0,ABC=0

F(A,B,C,D)=BD

(5)F(A,B,C,D)=ABC+ABC+ABCD+ABCD且ABCD不可同时为1或同时为0

F(A,B,C,D)=BD+AC

(6)F(A,B,C,D)=M(5,7,13,15)

F=B+D

(7)F(A,B,C,D)=M(1,3,9,10,14,15)

F=AD+AB+CD+BC+ABCD

(8)F(A,B,C,D,E)=m(0,4,5,6,7,8,11,13,15,16,20,21,22,23,24,25,27,29,31)

F=CDE+BC+CE+BDE+ABE

2.13用卡诺图将下列函数化为最简或与式

F=(A+B+C)(A+B+C)

(2)F(A,B,C)=M(5,7,13,15)

F=(B+D)

2.14已知:

F1(A,B,C)=m(1,2,3,5,7)+(0,6),F2(A,B,C)=m(0,3,4,6)+(2,5),求F=F1F2的最简与或式

F=A+B

4.1分析图4.1电路的逻辑功能

(1)推导输出表达式(略)

(2)列真值表(略)

(3)逻辑功能:

当M=0时,实现3位自然二进制码转换成3位循环码。

当M=1时,实现3位循环码转换成3位自然二进制码。

4.2分析图P4.2电路的逻辑功能。

(1)从输入端开始,逐级推导出函数表达式。

(略)

(2)列真值表。

(3)确定逻辑功能。

假设变量A、B、C和函数F1、F2均表示一位二进制数,那么,由真值表可知,该电路实现了一位全减器的功能。

A、B、C、F1、F2分别表示被减数、减数、来自低位的借位、本位差、本位向高位的借位。

4.3分析图4.3电路的逻辑功能

实现1位全加器。

4.4设ABCD是一个8421BCD码,试用最少与非门设计一个能判断该8421BCD码是否大于等于5的电路,该数大于等于5,F=1;

否则为0。

逻辑电路如下图所示:

4.5试设计一个2位二进制数乘法器电路。

为了使电路尽量简单,希望门数越少越好,本电路是四输出函数,圈卡诺圈时要尽量选择共有的卡诺圈以减少逻辑门的数量。

电路图略。

4.6试设计一个将8421BCD码转换成余3码的电路。

电路图略。

4.7在双轨输入条件下用最少与非门设计下列组合电路:

4.8在双轨输入信号下,用最少或非门设计题4.7的组合电路。

将表达式化简为最简或与式:

(1)F=(A+C)(A+B+C)=A+C+A+B+C

(2)F=(C+D)(B+D)(A+B+C)=C+D+B+D+A+B+C

(3)F=(A+C)(A+B+D)(A+B+D)=A+C+A+B+D+A+B+D

(4)F=(A+B+C)(A+B+C)=A+B+C+A+B+C

4.9已知输入波形A、B、C、D,如图P4.4所示。

采用与非门设计产生输出波形如F的组合电路。

F=AC+BC+CD电路图略

4.10电话室对3种电话编码控制,按紧急次序排列优先权高低是:

火警电话、急救电话、普通电话,分别编码为11,10,01。

试设计该编码电路。

4.11试将2/4译码器扩展成4/16译码器

A1ENY3

A02/4Y2

译码器Y1

Y0

A3

A2

EN

A12/4(4)

A0Y0Y1Y2Y3

A12/4

(2)

A12/4

(1)

A1

A0

A12/4(3)

Y0Y1Y2Y3Y4Y5Y6Y7Y8Y9Y10Y11Y12Y13Y14Y15

4.12试用74138设计一个多输出组合网络,它的输入是4位二进制码ABCD,输出为:

F1:

ABCD是4的倍数。

F2:

ABCD比2大。

F3:

ABCD在8~11之间。

F4:

ABCD不等于0。

电路如下图所示:

4.13试将八选一MUX扩展为六十四选一MUX。

方法一:

Y

Y7

Y6

Y1

Y0

D63

D57

D56

D55

D49

D48

D15

D9

D8

D7

D1

D0

A0

A1

A2

A3

A4

A5

A2Y0

A1Y1

A0Y2

74138Y3

E1Y4

E2AY5

E2BY6

Y7

³

EN

D174151(8)Y

D2

D3

D4

D5

D6

D174151(7)Y

D174151

(2)Y

D174151

(1)Y

方法一电路图

方法二:

方法二电路图

4.14试用74151实现下列函数:

(1)电路图如下所示:

(2)F(A,B,C)=AB+AB+C

D174151Y

A

C

F

(3)F(A,B,C,D)=ABC+BCD+ACD

D

D

令A=A2、B=A1、C=A0则:

D0=D7=D,D1=D,D6=1,D2=D3=D4=D5=0。

相应的电路图如下图所示:

(5)F(A,S,C,D,E)=ABCD+ABCE+BCDE

4.15用½

74153实现下列函数:

电路图如下:

(2)F(A,B,C)=m(1,2,4,7)

D0Y

D1

C

4.16试在图4.2.31的基础上增加一片7485,构成25位数据比较器。

=

A3A2A1A0B3B2B1B0

(A>

B)i

(A=B)i7485

(A<

FA>

BFA=BFA<

A20

B20

A24A23A22A21

B24B23B22B21

B5

A9A8A7A6

B9B8B7B6

B0

A4A3A2A1

B4B3B2B1

A10

B10

A14A13A12A11

B14B13B12B11

A15

B15

A19A18A17A16

B19B18B17B16

FA>

4.17设A=A3A2A1A0,B=B3B2B1B0均为8421BCD码。

试用74283设计一个A、B的求和电路。

(可用附加器件)

设COS3S2S1S0为A、B的二进制和,则当CO=1或S3S2S1S0>

1001时,须加0110修正项进行调整,计算结果为C4C3C2C1C0。

S0

S1

S2

S3

A1CO

A0S3

CI74283S2

B3S1

B2S0

B1

&

B2

B3

C4

C3

C2

C1

C0

4.18用74283将8421BCD码转换为余3BCD码。

电路图如右所示:

4.20用74283将8421BCD码转换为5421BCD码。

4.21设A=A3A2A1A0,B=B3B2B1B0是两个4位二进制数。

试用7485和74157(四二选一MUX)构成一个比较电路并能将其中大数输出。

试画出逻辑图。

4.22分析如下图所示的组合网络中,当ABCD从0100向1101变化时和ABCD从1000向1101变化时,是否会出现冒险?

试用增加多余项和取样脉冲的方法来避免冒险现象。

解:

1.当ABCD从0100向1101变化时:

电路中存在功能冒险。

2.当ABCD从1000向1101变化时:

电路中不存在功能冒险。

再判断是否有逻辑冒险:

AC=10时,存在0型逻辑冒险。

3.增加多余项的方法消除逻辑冒险:

4.加取样脉冲法避免冒险:

5.1基本触发器的逻辑符号与输入波形如图P5.1所示。

试作出Q、Q的波形。

图P5.1

5.2图P5.2电路,在开关S由A点拨到B点,再由B点拨回A点过程中,A、B两点电压波形如图中所示。

试作出Q和Q端的波形。

图P5.2

5.3分析图P5.3的逻辑功能:

列出真值表,导出特征方程并说明SD、RD的有效电平。

(1)列真值表如下

下略

5.4对于图P5.4电路,试导出其特征方程并说明对A、B的取值有无约束条件。

(1)列真值表如下下略

5.5试写出图P5.5触发器电路的特征方程。

CP=0时,Qn+1=Qn

图P5.5

5.6试写出图P5.6各触发器电路的特征方程。

图P5.6

(b)~(h)略

5.7维阻D触发器的CP和D信号如图P5.7所示,设触发器Q端的初态为“0”,试作Q端波形。

图P5.7图P5.8

5.8维阻D触发器构成的电路如图P5.8所示,试作Q端波形。

特征方程为:

,Q端波形如图P5.8所示。

5.10画出图P5.10中Q端的波形。

设初态为“0”。

Q端波形如图P5.10所示。

图P5.10

5.11画出图P5.11电路Q端的波形。

Q端波形如图P5.11所示。

图P5.11

P5.12

5.12画出图P5.12电路中Q1、Q2的波形。

Q端波形如图P5.12所示。

5.13画出图P5.13电路中Q1和Q2的波形。

图P5.13

5.14试作出图P5.14中Q端和Z端的波形。

设Q的初态为“0”。

Q、Z端波形如图P5.14所示。

图P5.14图P5.15

5.

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字电路 系统 设计 课后 习题 答案

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

整编新型生态农业旅游休闲农庄项目发展建设市场研究报告.docx

整编新型生态农业旅游休闲农庄项目发展建设市场研究报告.docx