Verilog RS232串口模块实验报告.docx

Verilog RS232串口模块实验报告.docx

- 文档编号:11146644

- 上传时间:2023-05-29

- 格式:DOCX

- 页数:12

- 大小:610.06KB

Verilog RS232串口模块实验报告.docx

《Verilog RS232串口模块实验报告.docx》由会员分享,可在线阅读,更多相关《Verilog RS232串口模块实验报告.docx(12页珍藏版)》请在冰点文库上搜索。

VerilogRS232串口模块实验报告

1设计概述

实验功能:

实现RS232的双工通信。

实验环境:

1)硬件环境:

PC机一台、ml507PFGA开发套件;2)软件环境:

开发软件ISE14.5、代码编写软件Notepad++、仿真软件Modelsim、调试软件chipscope、串口调试工具。

2设计原理

2.1串行接口RS232工作原理

串口用来连接FPGA和PC机,RS-232允许全双工通信,即计算机在接收数据的同时可以发送数据。

串口按位(bit)发送和接收字节。

通常以8位数据为1组,先发送最低有效位,最后发送最高有效位。

尽管比按字节(byte)的并行通信慢,但是串口可以在使用一根线发送数据的同时用另一根线接收数据。

通信使用3根线完成:

(1)地线,

(2)发送,(3)接收。

由于串口通信是异步的,端口能够在一根线上发送数据同时在另一根线上接收数据。

其他线用于握手,但不是必须的。

数据的传输没有时钟信号,接收端必须采取某种方式,使之与接收数据同步。

1)串行线缆的两端先约定好串行传输的参数(传输速度、传输格式等);

2)当没有数据传输的时候,发送端向数据线上发送"1";

3)每传输一个字节之前,发送端先发送一个"0"来表示传输已经开始,这样接收端便可以知道有数据到来了;

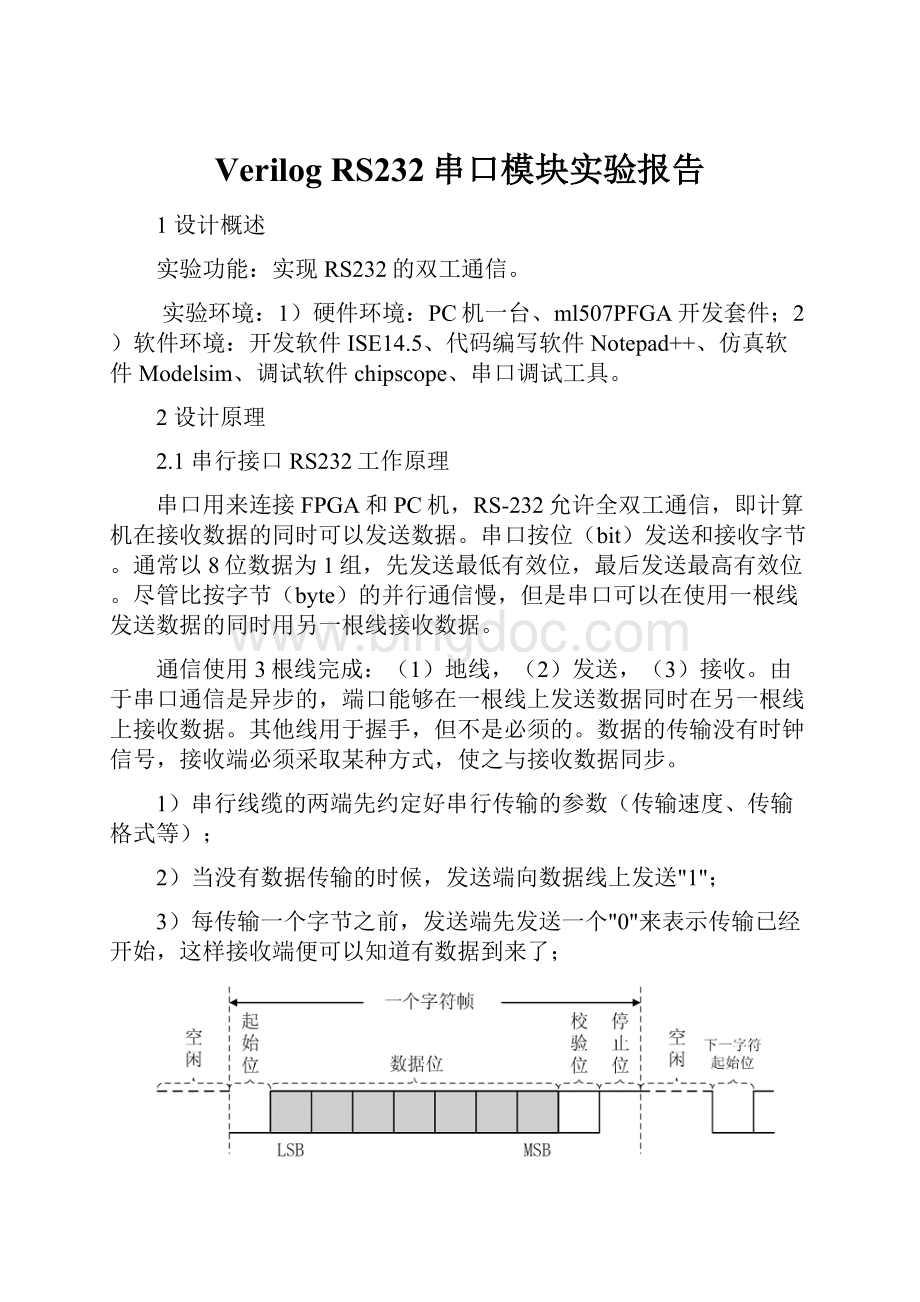

图1数据帧结构

4)开始传输后,数据以约定的速度和格式传输,所以接收端可以与之同步;

5)在串口总线上‘高电平’是默认的状态,当一帧数据开始传输必须先拉低电平,这就是起始位,起始位之后是8位数据位,最后是校验位和停止位(可不加校验位)。

传输完成一个字节之后,都在其后发送一个停止位("1")。

(图1)

2.2波特率发生器

波特率是串口传输的传输速度;在微观上就是一个位的周期。

常用的波特率有9600bps和115200bps。

“9600bps”表示每秒可以传输9600位。

本次实验我所选用的传输速率为9600bps。

由于我们的FPGA通常运行在远高于9600Hz的频率上(100MHz),因此需要分频产生接近9600Hz的时钟信号。

若FPGA时钟为100MHz,则需要100M/9600=10416个时钟周期置位一次就可以得到9600Hz的时钟。

3模块组成

3.1接收模块

接收模块示意图(图2)

图2接收模块示意图

串口接收包括三个模块:

电平检测模块,用来检测数据开始,当检测到输入信号RX_Pin_In有下降沿时,可以判断信号到来,H2L_Sig信号输出为高电平通知接收控制模块准备接收数据;波特率定时模块,用来产生波特率(9600bps);接收控制模块,用来控制接收开始和结束。

RX_En_Sig为高电平时,若电平检测模块检测到有数据输入,则发出H2L_Sig高电平信号,接收控制模块输出Count_Sig信号,波特率定时模块开始计数。

为了确保采集到的数据的准确性,数据采集都是在每位数据的中间进行着(图3)。

为使采集信号出现在数据位中间,决定每次计数到5208产生一个采集信号BPS_CLK,持续一个时钟周期,计数到10416时计数器清零并重新计数,这样采集信号周期不变,准确度提高。

图3数据定时采集示意图

接收控制模块将8位数据位并行输出,输出RX_Done_Sig信号表示一帧数据结束,发送模块可以接收来自RX_Data的数据。

3.1.1detect_module.v

detect_module.v这个功能模块是为了检查电平由高变低。

当检测到电平又高变低,在第40行就会输出高脉冲。

3.1.2rx_bps_module.v

波特率定时模块,用来产生波特率,其原理同计数器。

当rx_control_module.v拉高Count_Sig,bps_module.v经BPS_CLK对rx_control_module.v产生定时。

3.1.3rx_control_module.v

rx_control_module.v是核心控制模块,用来控制接收开始和结束。

对串口的配置主要是1帧11位的数据,重视八位数据位,无视起始位,校验位和结束位。

当RX_En_Sig拉高,这个模块就开始工作,它将采集来自RX_Pin_In的数据,当完成一帧数据接收的时候,就会产生一个高脉冲给RX_Done_Sig。

44~62行是rx_control_module.v的核心控制功能。

当rx_control_module.v模块被使能,该模块就会处于就绪状态,一旦detect_module.v检查到又高变低的电平变化(47行),会使步骤i进入第0位采集,然而isCount标志寄存器同时也会被设置为逻辑1,rx_bps_module.v便会开始产生波特率的定时。

3.1.4rx_module.v

rx_module.v是一个组合模块,主要是包含detect_module.v,bps_module.v和rx_control_module.v,2个功能模块,和1个组合模块。

完成对三个模块的例化及信号传递。

3.2发送模块

发送模块示意图(图4)

图4发送模块示意图

发送模块包括波特率定时模块,当TX_En_Sig低电平时不工作,高电平时开始计数,然后产生一个高脉冲经BPS_CLK输出给发送控制模块;发送控制模块在TX_En_Sig高电平时,每收到一个BPS_CLK,将TX_Data的数据,由TX_Pin_Out输出。

当一帧数据发送完毕后,产生一个TX_Done_Sig的高脉冲(图5)。

图5数据定时发送示意图

3.2.1tx_bps_module.v

tx_bps_module.v同样是作为“定时”的功能。

当TX_En_Sig拉低电平的时候,它是处于随眠的状态。

一旦TX_En_Sig拉高电平,那么tx_bps_module.v就开始计数。

然后定时产生一个高脉冲经BPS_CLK给tx_control_module.v。

程序与rx_bps_module.v基本相同。

3.2.2tx_control_module.v

tx_control_module.v控制模块是最为中心的一部分,当TX_En_Sig拉高电平,同时间tx_bps_module.v也会开始计数。

tx_control_module.v将TX_Data的值,按tx_bps_module.v产生的定时,有节奏的往TX_Pin_Out发送。

当一帧数据发送完毕后,就产生一个TX_Done_Sig的高脉冲。

3.2.3tx_module.v

4功能仿真

4.1接收模块仿真

4.1.1接收模块验证程序

增加一个control_module.v模块,一开始control_module.v会拉高RX_En_Sig使能rx_module.v。

当有一阵数据经RX_Pin_In传入,rx_module.v就会接收然后将输出输出致RX_Data,再产生一个高脉冲给RX_Done_Sig。

当control_module.v接收到RX_Done_Sig的高脉冲,就会将RX_Data的“前四位”输出致4位LED资源。

rx_module_demo.v为一组合模块,完成对control_module.v和rx_module.v的例化。

tb_RX_DATA.v为测试文件。

1)control_module.v

一开始的时候(36行)就将isEn设置为逻辑1,这个标志寄存器在38行驱动着RX_En_Sig,即此时的rx_module.v已经进入就绪状态,control_module.v等待着RX_Done_Sig的通知(34行)。

一旦一帧数据接收完毕,RX_Done_Sig就会产生高脉冲,然后rData被赋予RX_Data的值,同时isEn被设置为逻辑0(35行)。

在下一瞬间,control_module.v再一次设置isEn为逻辑1,做好接收下一组数据的准备。

2)rx_module_demo.v(略)

3)tb_RX_DATA.v

测试文件输出的数据为“1111_1111”。

4.1.2Modelsim的仿真

仿真结果(图6)

图6接收模块验证仿真结果

可以看出,该程序能够正确判断数据帧的起始位和终止位,正确接收了数据帧“1111_1111”,并将高四位赋给了Number_Data,来控制四个LED灯。

4.2发送模块仿真

4.2.1发送模块验证程序

增加一个control_module.v模块,主要是每秒往tx_module.v发送0x31的数据。

一开始control_module.v往TX_Data输出数据,然后拉高TX_Done_Sig使tx_module.v开始工作。

当tx_module.v发往一帧数据以后,就会对TX_Done_Sig产生一个高脉冲,以示发送完毕。

tx_module_demo.v为一组合模块,完成对control_module.v和tx_module.v的例化。

tb_TX_DATA.v为测试文件。

1)control_module.v

第28行是1秒的定义常量,在30~36行是1秒的定时器。

control_module.v主要是每秒发送0x31的数据,也就是每秒设置一次isEn标志寄存器。

当isEn被设置后,tx_module.v就会开始工作,发完一帧数据位TX_Done_Sig会产生高脉冲。

这使得control_module.v会重新赋值rData寄存器,然后复位isEn标志寄存器。

直到下一秒的到来,isEn标志寄存器会再一次被设置。

2)tx_module.v(略)

3)tb_TX_DATA.v

4.2.2实验仿真

为了便于仿真,将常量T1S=25’d19_999。

仿真结果(图7)

图7发送模块验证仿真结果

可以看出,TX_Pin_Out正确发送起始位“0”,数据位“1000_1100”,终止位“1”。

5总结

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- Verilog RS232串口模块实验报告 RS232 串口 模块 实验 报告

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《大侦探小卡莱》读后感.docx

《大侦探小卡莱》读后感.docx